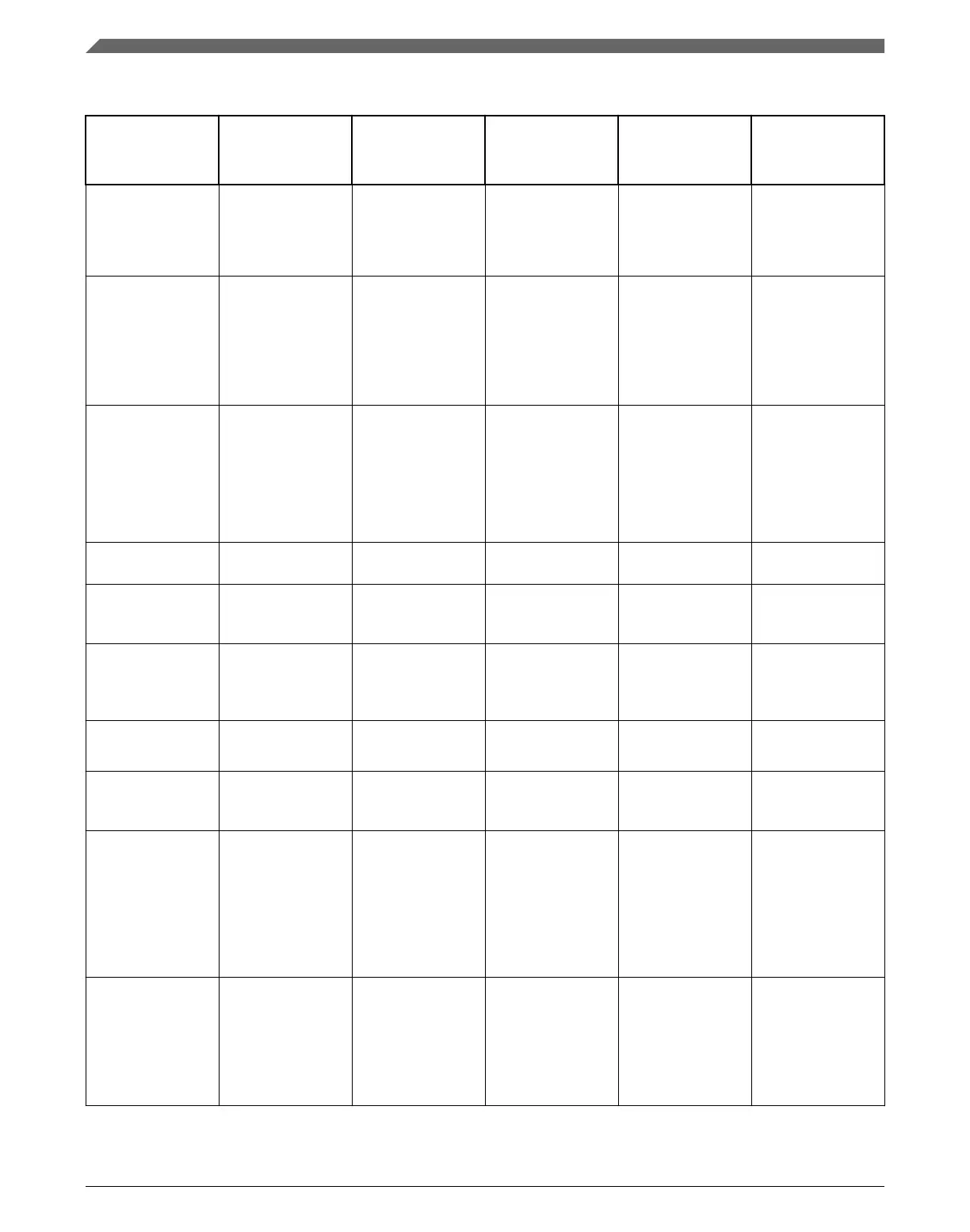

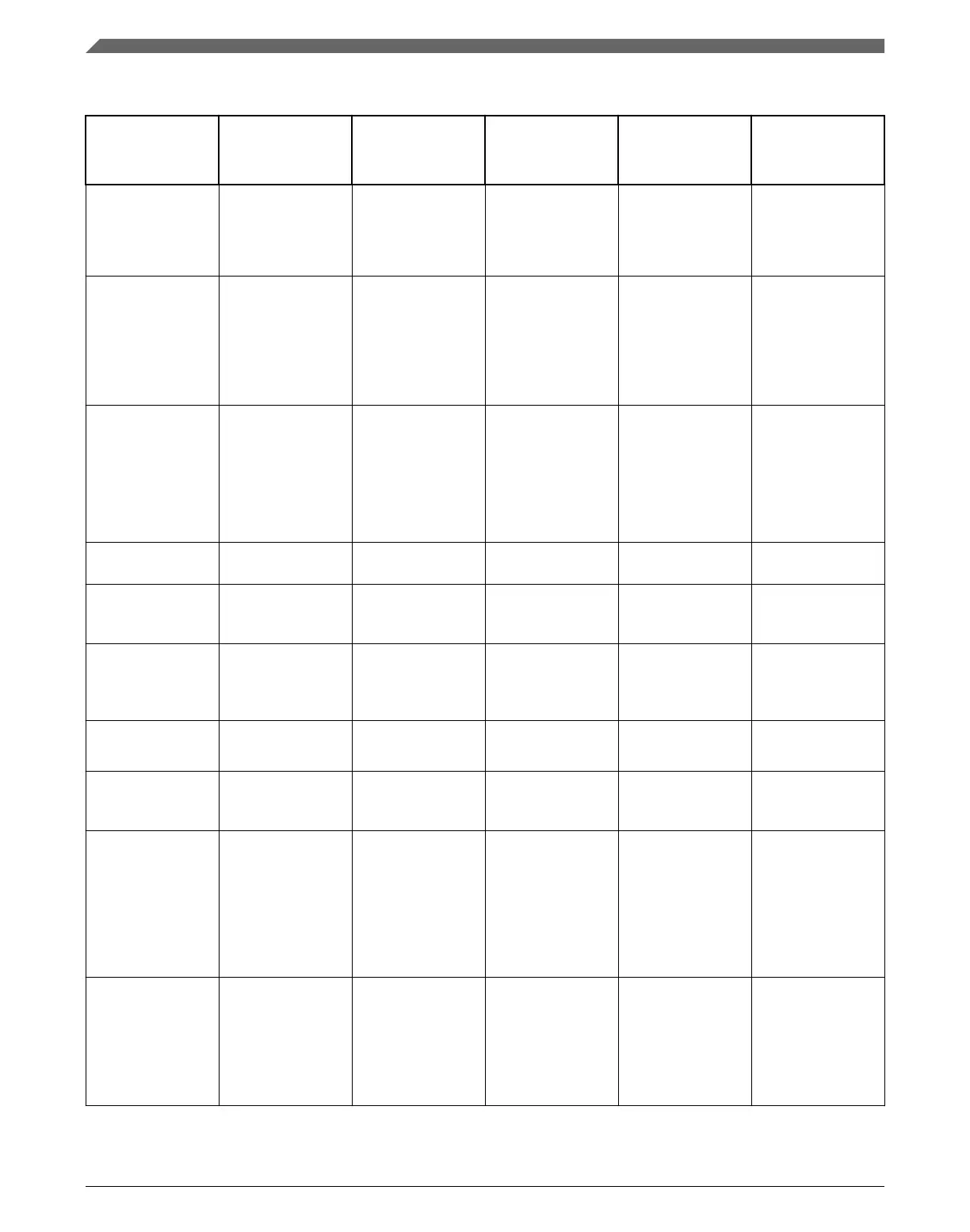

Table 5-1. Clock Summary (continued)

Clock name High Speed Run

mode

clock frequency

Run mode

clock frequency

VLPR mode

clock frequency

Clock source Clock is disabled

when…

stop modes and

during PLL locking

when

MCGOUTCLK

derived from PLL.

MCGFLLCLK Up to 100 MHz Up to 100 MHz N/A MCG MCG clock controls

do not enable.

Overriding forced

disable in all low

powers modes

(including STOP

and VLPx modes).

MCGPLLCLK Up to 120 MHz Up to 120 MHz N/A MCG MCG clock controls

do not enable,

in Stop mode but

PLLSTEN=0,

or in VLPS, LLS

and VLLSx modes

Core clock Up to 120 MHz Up to 80 MHz Up to 4 MHz MCGOUTCLK

clock divider

In all wait and stop

modes

System clock Up to 120 MHz Up to 80 MHz Up to 4 MHz MCGOUTCLK

clock divider

In all stop modes

and Compute

Operation

Bus clock Up to 60 MHz Up to 50 MHz Up to 4 MHz MCGOUTCLK

clock divider

In all stop modes

except for partial

STOP2 mode, and

Compute Operation

FlexBus clock

(FB_CLK)

Up to 30 MHz Up to 30 MHz Up to 4 MHz MCGOUTCLK

clock divider

In all stop modes or

FlexBus disabled

Flash clock Up to 26.67 MHz Up to 26.67 MHz Up to 1 MHz in

BLPE, Up to 800

kHz in BLPI

MCGOUTCLK

clock divider

In all stop modes

except for partial

STOP2 mode

Internal reference

(MCGIRCLK)

30-40 kHz or 4

MHz

30-40 kHz or 4

MHz

4 MHz only MCG MCG_C1[IRCLKEN

] cleared,

Stop or VLPS

mode and

MCG_C1[IREFSTE

N] cleared, or

LLS/VLLS mode

External reference

(OSCERCLK)

Up to 50 MHz

(bypass),

30-40 kHz, or

3-32 MHz (crystal)

Up to 50 MHz

(bypass),

30-40 kHz, or

3-32 MHz (crystal)

Up to 16 MHz

(bypass),

30-40 kHz (low-

range crystal) or

Up to 16 MHz

(high-range crystal)

System OSC System OSC's

OSC_CR[ERCLKE

N] cleared, or

Stop mode and

OSC_CR[EREFST

EN] cleared

Table continues on the next page...

Clock definitions

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

154 NXP Semiconductors

Loading...

Loading...