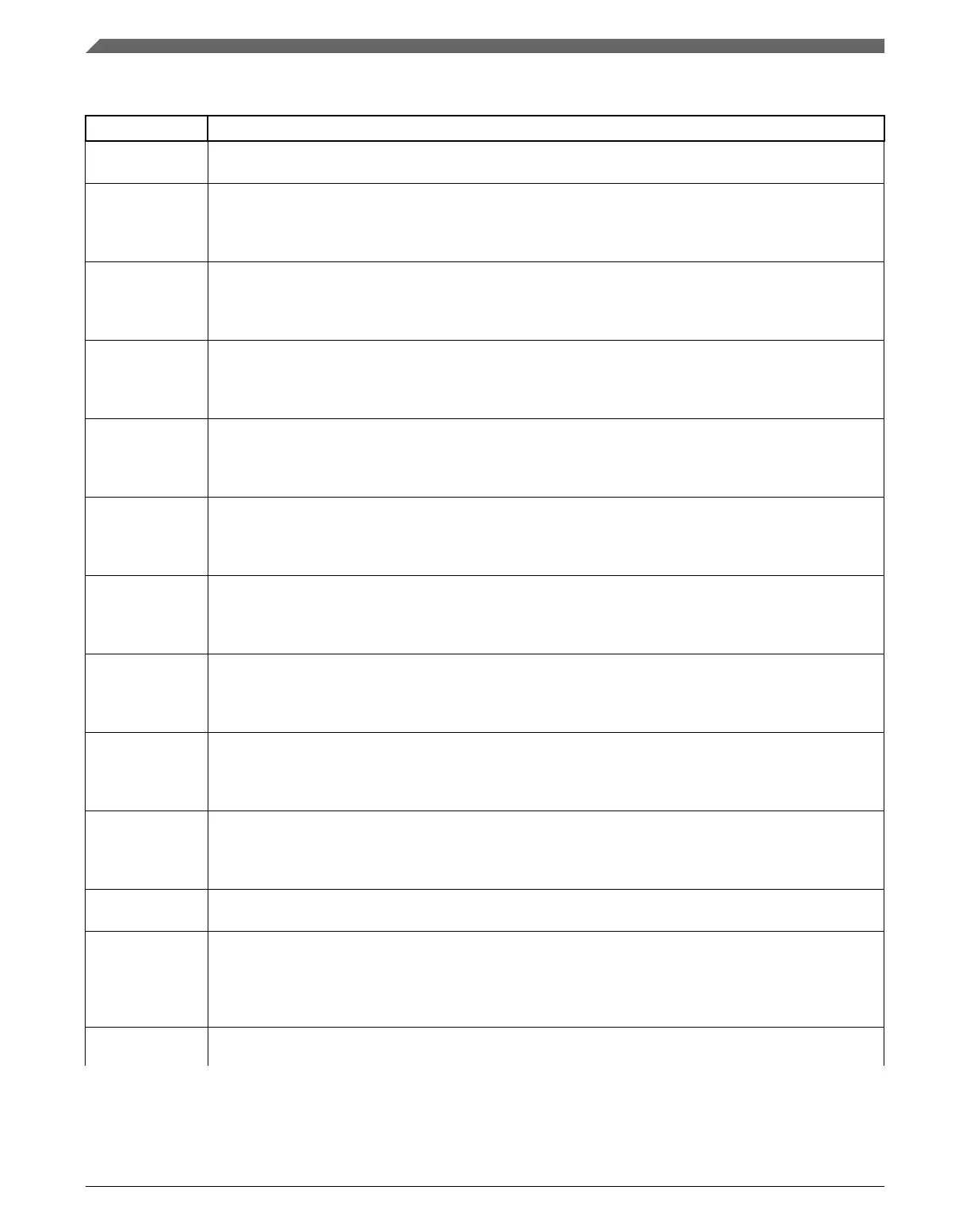

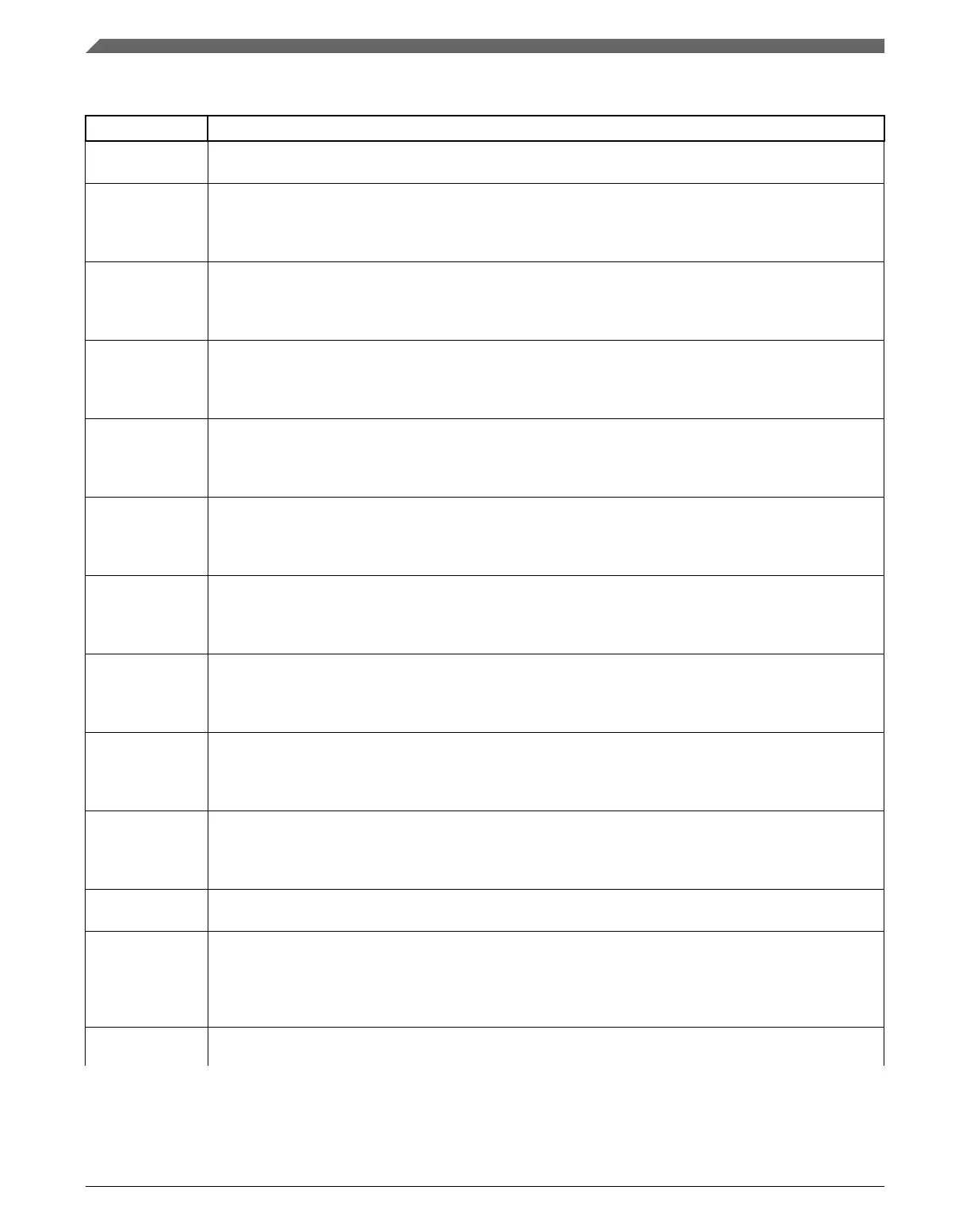

SIM_SOPT8 field descriptions (continued)

Field Description

0 FTM3_CH1 pin is output of FTM3 channel 1 output

1 FTM3_CH1 pin is output of FTM3 channel 1 output modulated by FTM2 channel 1 output.

24

FTM3OCH0SRC

FTM3 channel 0 output source

0 FTM3_CH0 pin is output of FTM3 channel 0 output

1 FTM3_CH0 pin is output of FTM3 channel 0 output modulated by FTM2 channel 1 output.

23

FTM0OCH7SRC

FTM0 channel 7 output source

0 FTM0_CH7 pin is output of FTM0 channel 7 output

1 FTM0_CH7 pin is output of FTM0 channel 7 output, modulated by FTM1 channel 1 output

22

FTM0OCH6SRC

FTM0 channel 6 output source

0 FTM0_CH6 pin is output of FTM0 channel 6 output

1 FTM0_CH6 pin is output of FTM0 channel 6 output, modulated by FTM1 channel 1 output

21

FTM0OCH5SRC

FTM0 channel 5 output source

0 FTM0_CH5 pin is output of FTM0 channel 5 output

1 FTM0_CH5 pin is output of FTM0 channel 5 output, modulated by FTM1 channel 1 output

20

FTM0OCH4SRC

FTM0 channel 4 output source

0 FTM0_CH4 pin is output of FTM0 channel 4 output

1 FTM0_CH4 pin is output of FTM0 channel 4 output, modulated by FTM1 channel 1 output

19

FTM0OCH3SRC

FTM0 channel 3 output source

0 FTM0_CH3 pin is output of FTM0 channel 3 output

1 FTM0_CH3 pin is output of FTM0 channel 3 output, modulated by FTM1 channel 1 output

18

FTM0OCH2SRC

FTM0 channel 2 output source

0 FTM0_CH2 pin is output of FTM0 channel 2 output

1 FTM0_CH2 pin is output of FTM0 channel 2 output, modulated by FTM1 channel 1 output

17

FTM0OCH1SRC

FTM0 channel 1 output source

0 FTM0_CH1 pin is output of FTM0 channel 1 output

1 FTM0_CH1 pin is output of FTM0 channel 1 output, modulated by FTM1 channel 1 output

16

FTM0OCH0SRC

FTM0 channel 0 output source

0 FTM0_CH0 pin is output of FTM0 channel 0 output

1 FTM0_CH0 pin is output of FTM0 channel 0 output, modulated by FTM1 channel 1 output

15–4

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

3

FTM3SYNCBIT

FTM3 Hardware Trigger 0 Software Synchronization

0 No effect.

1 Write 1 to assert the TRIG0 input to FTM3, software must clear this bit to allow other trigger sources

to assert.

2

FTM2SYNCBIT

FTM2 Hardware Trigger 0 Software Synchronization

Table continues on the next page...

Memory map and register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

274 NXP Semiconductors

Loading...

Loading...