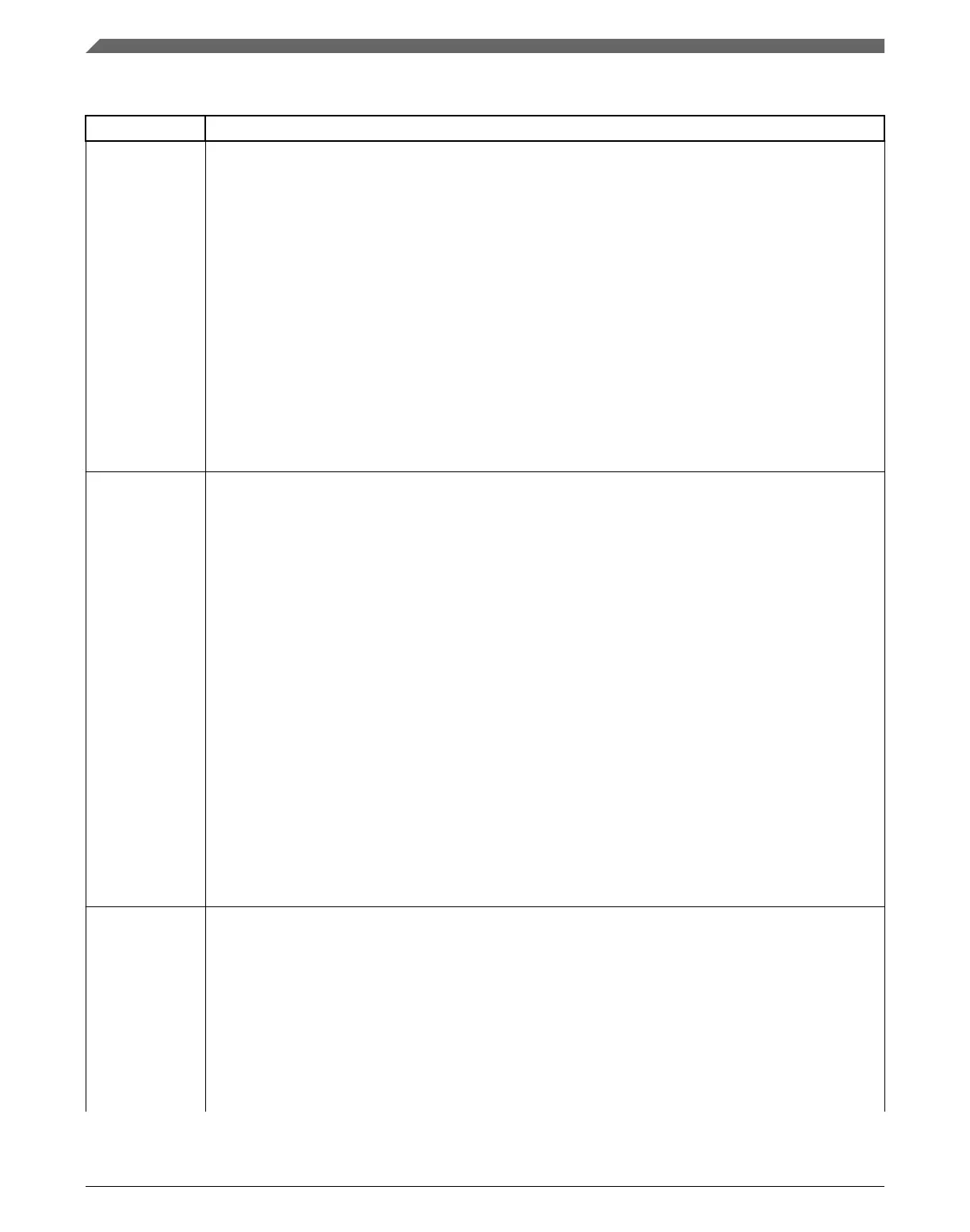

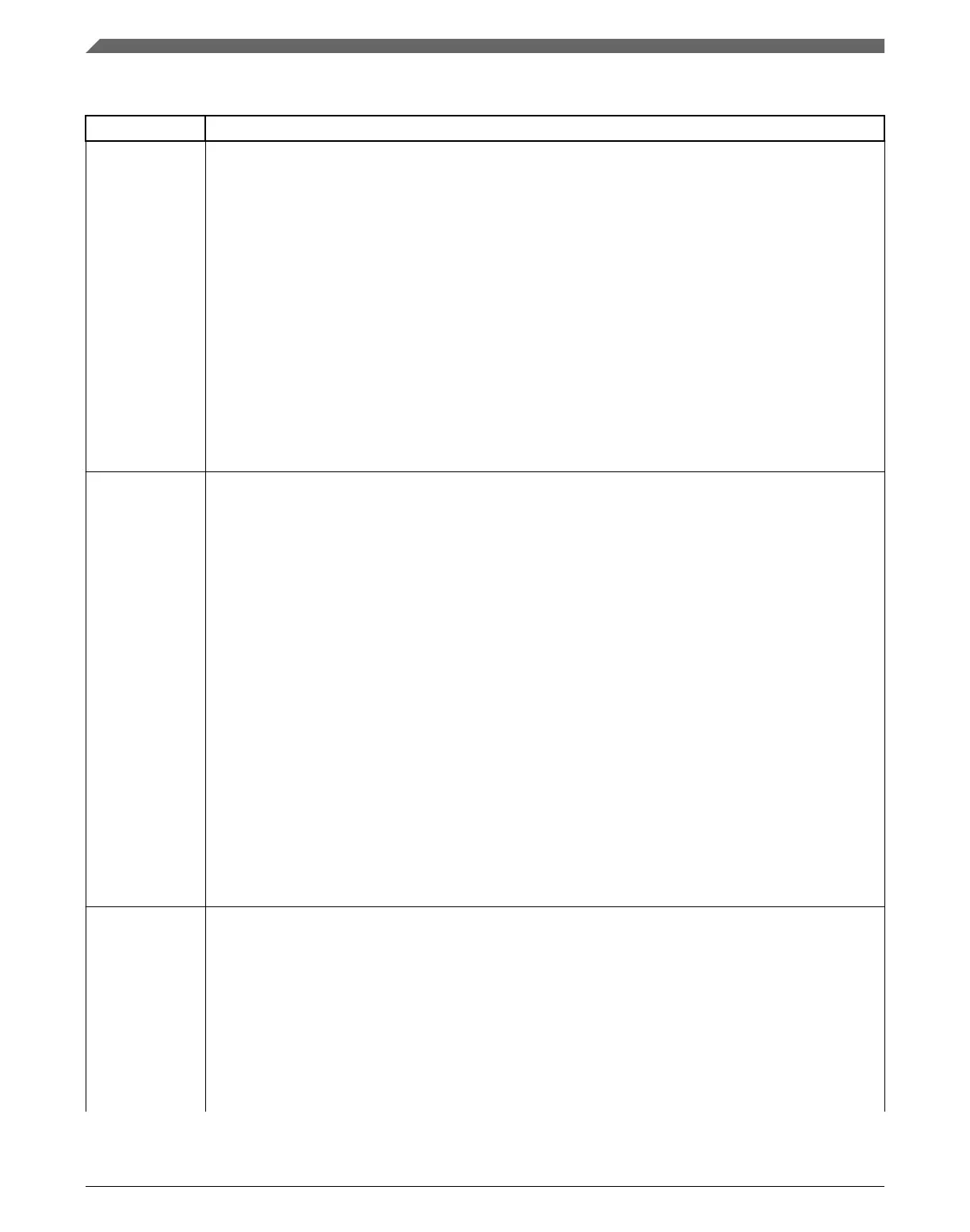

SIM_CLKDIV1 field descriptions (continued)

Field Description

0000 Divide-by-1.

0001 Divide-by-2.

0010 Divide-by-3.

0011 Divide-by-4.

0100 Divide-by-5.

0101 Divide-by-6.

0110 Divide-by-7.

0111 Divide-by-8.

1000 Divide-by-9.

1001 Divide-by-10.

1010 Divide-by-11.

1011 Divide-by-12.

1100 Divide-by-13.

1101 Divide-by-14.

1110 Divide-by-15.

1111 Divide-by-16.

23–20

OUTDIV3

Clock 3 output divider value

This field sets the divide value for the FlexBus clock (external pin FB_CLK) from MCGOUTCLK. At the

end of reset, it is loaded with either 0001 or 1111 depending on FTF_FOPT[LPBOOT]. The FlexBus clock

frequency must be an integer divide of the system clock frequency.

0000 Divide-by-1.

0001 Divide-by-2.

0010 Divide-by-3.

0011 Divide-by-4.

0100 Divide-by-5.

0101 Divide-by-6.

0110 Divide-by-7.

0111 Divide-by-8.

1000 Divide-by-9.

1001 Divide-by-10.

1010 Divide-by-11.

1011 Divide-by-12.

1100 Divide-by-13.

1101 Divide-by-14.

1110 Divide-by-15.

1111 Divide-by-16.

19–16

OUTDIV4

Clock 4 output divider value

This field sets the divide value for the flash clock from MCGOUTCLK. At the end of reset, it is loaded with

either 0001 or 1111 depending on FTF_FOPT[LPBOOT]. The flash clock frequency must be an integer

divide of the system clock frequency.

0000 Divide-by-1.

0001 Divide-by-2.

0010 Divide-by-3.

0011 Divide-by-4.

0100 Divide-by-5.

Table continues on the next page...

Memory map and register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

286 NXP Semiconductors

Loading...

Loading...