The following table shows the translation between the ARM CPU modes and the Kinetis

MCU power modes.

ARM CPU mode MCU mode

Sleep Wait

Deep Sleep Stop

Accordingly, the ARM CPU documentation refers to sleep and deep sleep, while the

Kinetis MCU documentation normally uses wait and stop.

In addition, Kinetis MCUs also augment Stop, Wait, and Run modes in a number of

ways. The power management controller (PMC) contains a run and a stop mode

regulator. Run regulation is used in normal run, wait and stop modes. Stop mode

regulation is used during all very low power and low leakage modes. During stop mode

regulation, the bus frequencies are limited in the very low power modes.

The SMC provides the user with multiple power options. The Very Low Power Run

(VLPR) mode can drastically reduce run time power when maximum bus frequency is

not required to handle the application needs. From Normal Run mode, the Run Mode

(RUNM) field can be modified to change the MCU into VLPR mode when limited

frequency is sufficient for the application. From VLPR mode, a corresponding wait

(VLPW) and stop (VLPS) mode can be entered.

Depending on the needs of the user application, a variety of stop modes are available that

allow the state retention, partial power down or full power down of certain logic and/or

memory. I/O states are held in all modes of operation. Several registers are used to

configure the various modes of operation for the device.

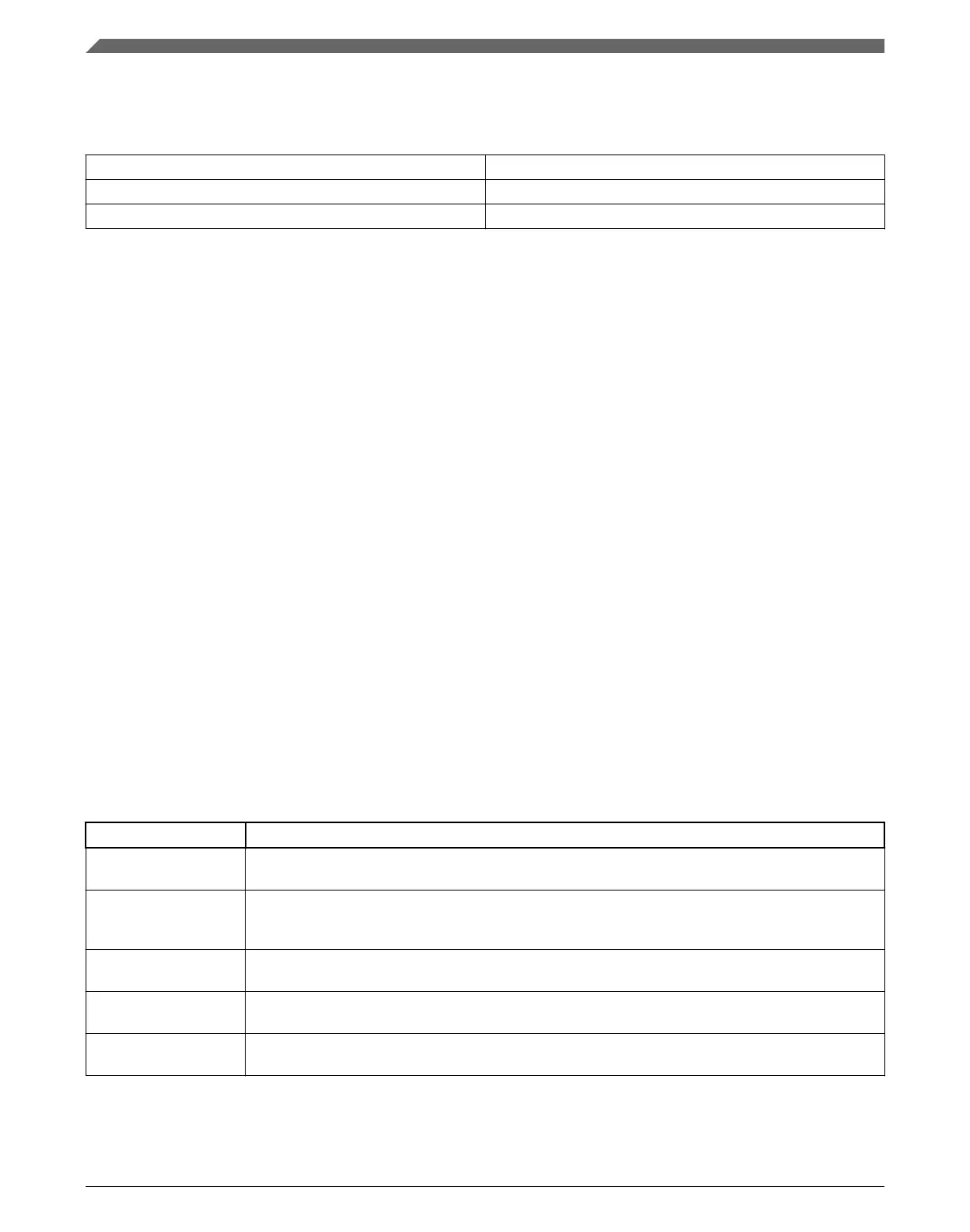

The following table describes the power modes available for the device.

Table 15-1. Power modes

Mode Description

RUN The MCU can be run at full speed and the internal supply is fully regulated, that is, in run regulation.

This mode is also referred to as Normal Run mode.

HSRUN The MCU can be run at a faster frequency compared with RUN mode and the internal supply is fully

regulated. See the Power Management chapter for details about the maximum allowable

frequencies.

WAIT The core clock is gated off. The system clock continues to operate. Bus clocks, if enabled, continue

to operate. Run regulation is maintained.

STOP The core clock is gated off. System clocks to other masters and bus clocks are gated off after all

stop acknowledge signals from supporting peripherals are valid.

VLPR The core, system, bus, and flash clock maximum frequencies are restricted in this mode. See the

Power Management chapter for details about the maximum allowable frequencies.

Table continues on the next page...

Modes of operation

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

352 NXP Semiconductors

Loading...

Loading...