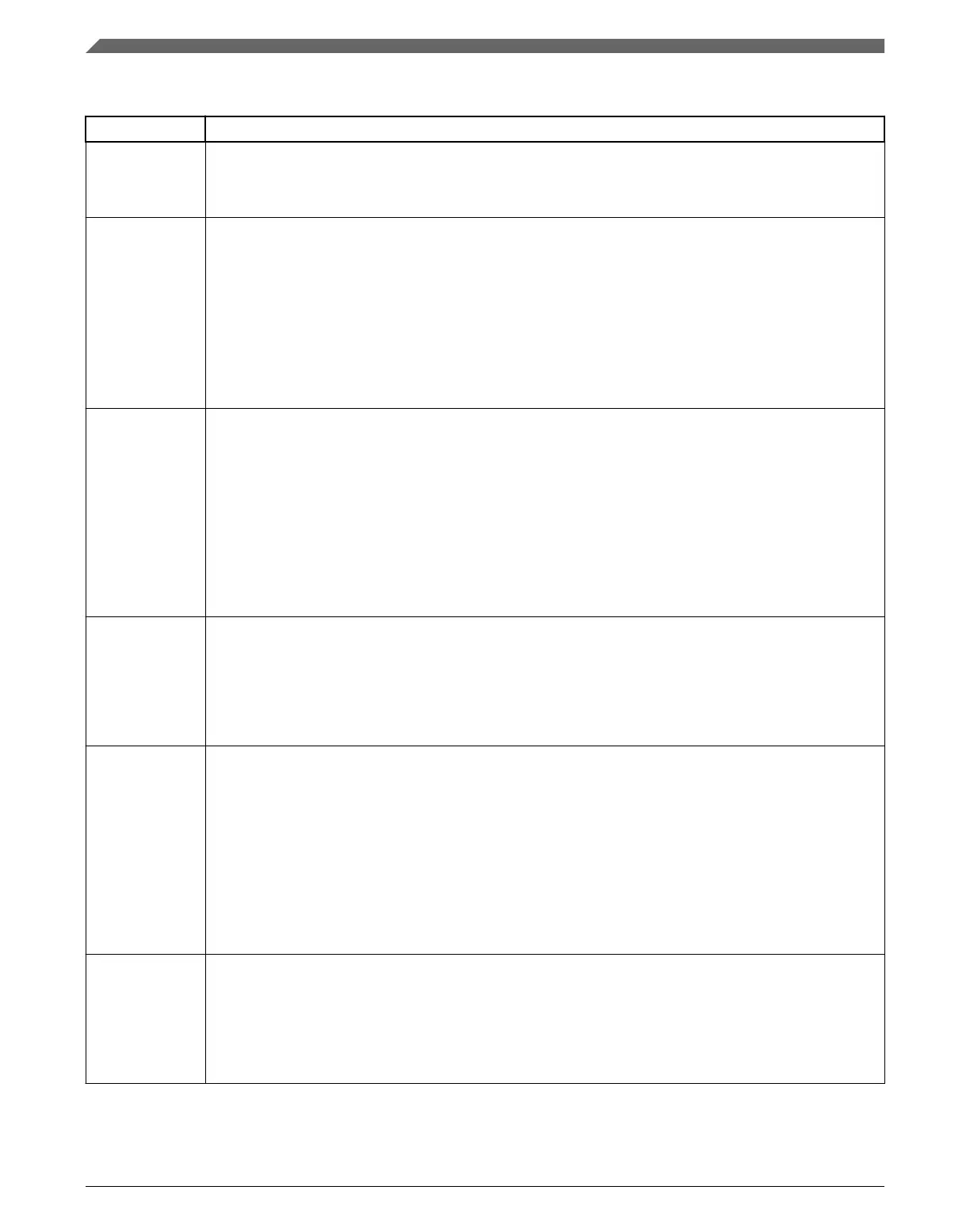

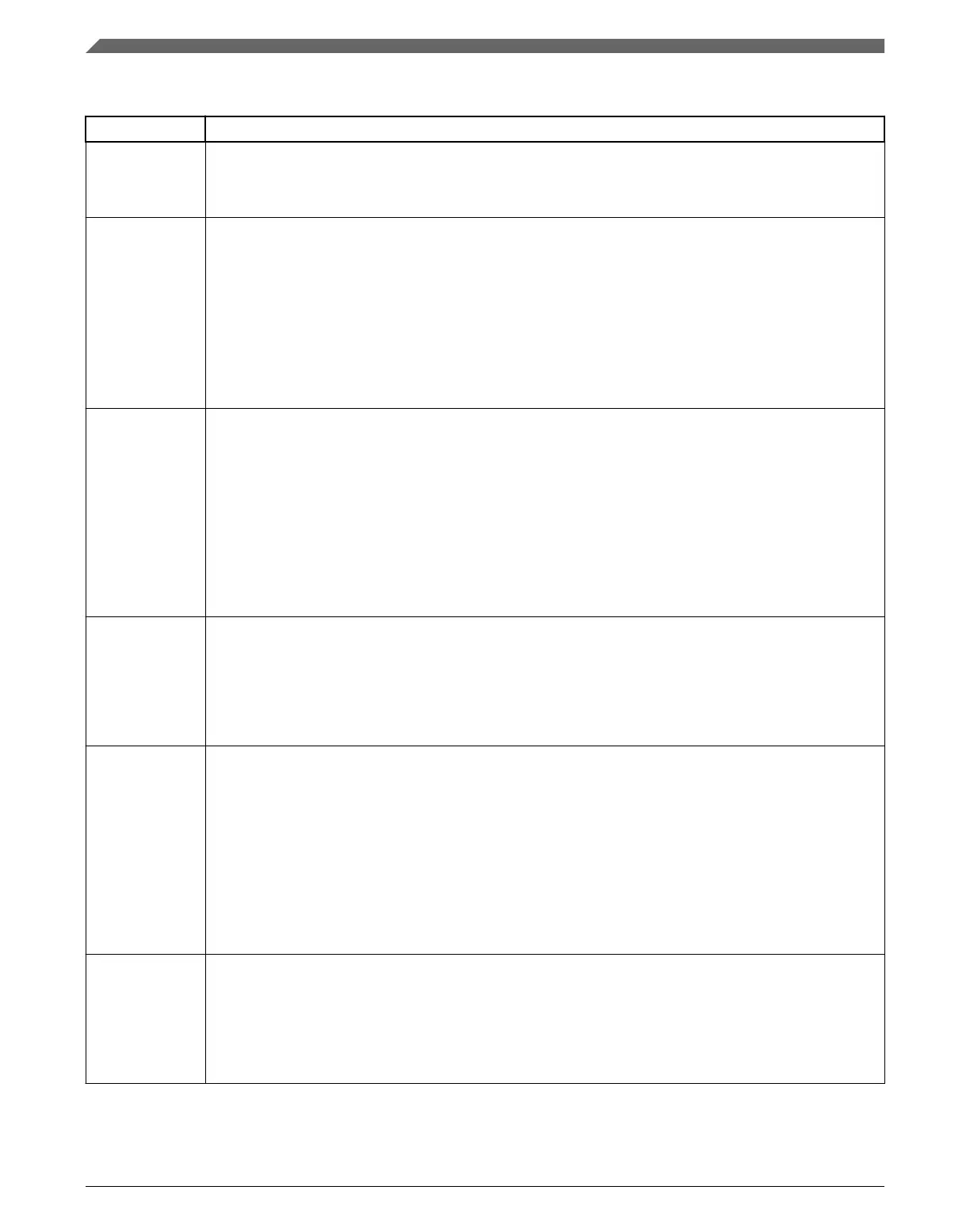

DMA_TCDn_CSR field descriptions (continued)

Field Description

6

ACTIVE

Channel Active

This flag signals the channel is currently in execution. It is set when channel service begins, and is cleared

by the eDMA as the minor loop completes or when any error condition is detected.

5

MAJORELINK

Enable channel-to-channel linking on major loop complete

As the channel completes the major loop, this flag enables the linking to another channel, defined by

MAJORLINKCH. The link target channel initiates a channel service request via an internal mechanism that

sets the TCDn_CSR[START] bit of the specified channel.

NOTE:

To support the dynamic linking coherency model, this field is forced to zero when written to while

the TCDn_CSR[DONE] bit is set.

0 The channel-to-channel linking is disabled.

1 The channel-to-channel linking is enabled.

4

ESG

Enable Scatter/Gather Processing

As the channel completes the major loop, this flag enables scatter/gather processing in the current

channel. If enabled, the eDMA engine uses DLASTSGA as a memory pointer to a 0-modulo-32 address

containing a 32-byte data structure loaded as the transfer control descriptor into the local memory.

NOTE:

To support the dynamic scatter/gather coherency model, this field is forced to zero when written

to while the TCDn_CSR[DONE] bit is set.

0 The current channel’s TCD is normal format.

1 The current channel’s TCD specifies a scatter gather format. The DLASTSGA field provides a memory

pointer to the next TCD to be loaded into this channel after the major loop completes its execution.

3

DREQ

Disable Request

If this flag is set, the eDMA hardware automatically clears the corresponding ERQ bit when the current

major iteration count reaches zero.

0 The channel’s ERQ bit is not affected.

1 The channel’s ERQ bit is cleared when the major loop is complete.

2

INTHALF

Enable an interrupt when major counter is half complete.

If this flag is set, the channel generates an interrupt request by setting the appropriate bit in the INT

register when the current major iteration count reaches the halfway point. Specifically, the comparison

performed by the eDMA engine is (CITER == (BITER >> 1)). This halfway point interrupt request is

provided to support double-buffered, also known as ping-pong, schemes or other types of data movement

where the processor needs an early indication of the transfer’s progress.

NOTE:

If BITER = 1, do not use INTHALF. Use INTMAJOR instead.

0 The half-point interrupt is disabled.

1 The half-point interrupt is enabled.

1

INTMAJOR

Enable an interrupt when major iteration count completes.

If this flag is set, the channel generates an interrupt request by setting the appropriate bit in the INT when

the current major iteration count reaches zero.

0 The end-of-major loop interrupt is disabled.

1 The end-of-major loop interrupt is enabled.

Table continues on the next page...

Memory map/register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

480 NXP Semiconductors

Loading...

Loading...