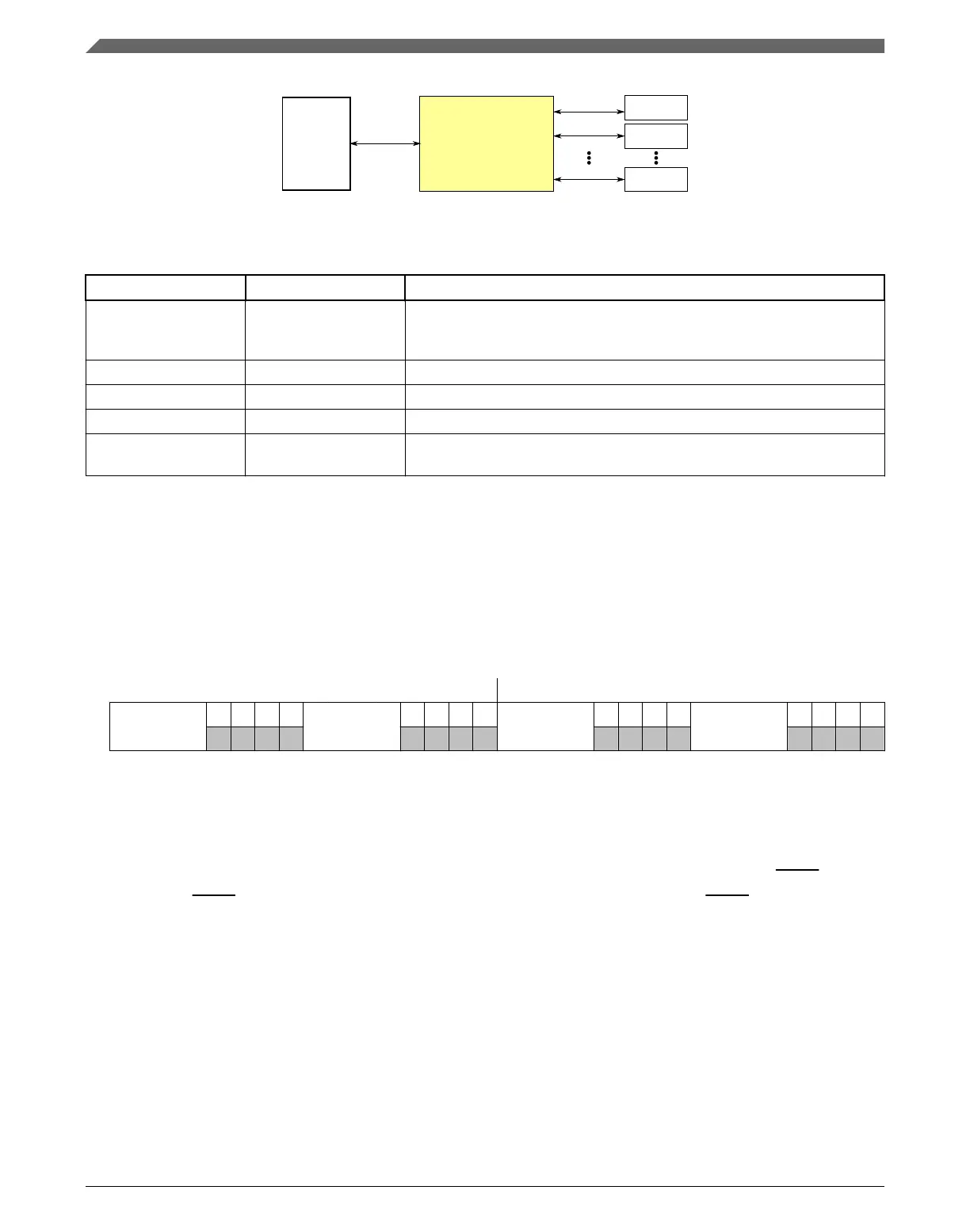

Nested Vectored

Interrupt Controller

(NVIC)

ARM

Cortex-M4

core

Interrupts

Module

Module

Module

PPB

Figure 3-2. NVIC configuration

Table 3-2. Reference links to related information

Topic Related module Reference

Full description Nested Vectored

Interrupt Controller

(NVIC)

ARM Cortex-M4 Technical Reference Manual

System memory map System memory map

Clocking Clock distribution

Power management Power management

Private Peripheral Bus

(PPB)

ARM Cortex-M4 core ARM Cortex-M4 core

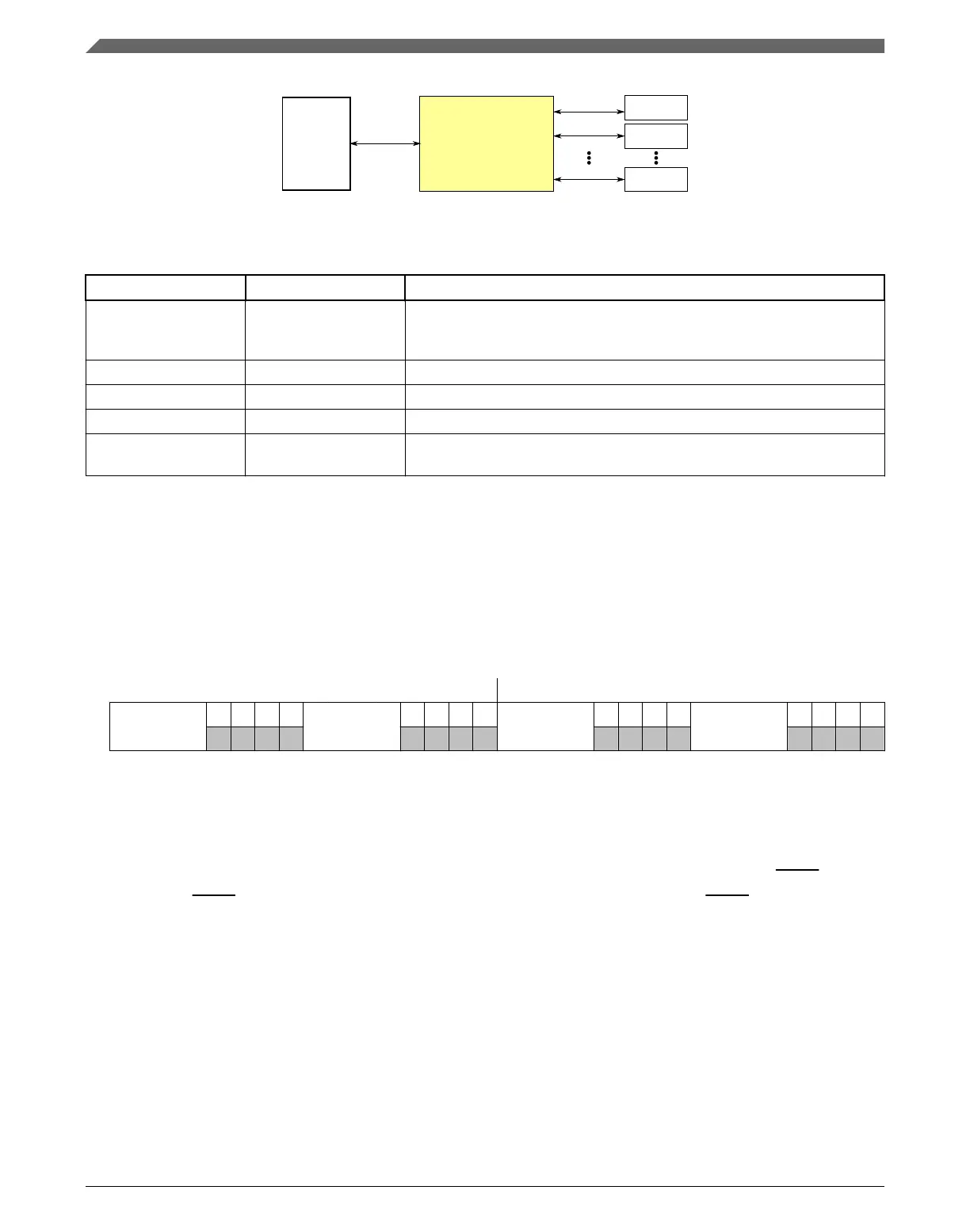

3.2.2.1 Interrupt priority levels

This device supports 16 priority levels for interrupts. Therefore, in the NVIC each source

in the IPR registers contains 4 bits. For example, IPR0 is shown below:

31

30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

IRQ3

0 0 0 0

IRQ2

0 0 0 0

IRQ1

0 0 0 0

IRQ0

0 0 0 0

W

3.2.2.2 Non-maskable interrupt

The non-maskable interrupt request to the NVIC is controlled by the external NMI signal.

The pin the NMI signal is multiplexed on, must be configured for the NMI function to

generate the non-maskable interrupt request.

3.2.2.3

Interrupt channel assignments

The interrupt source assignments are defined in the following table.

Core modules

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

60 NXP Semiconductors

Loading...

Loading...