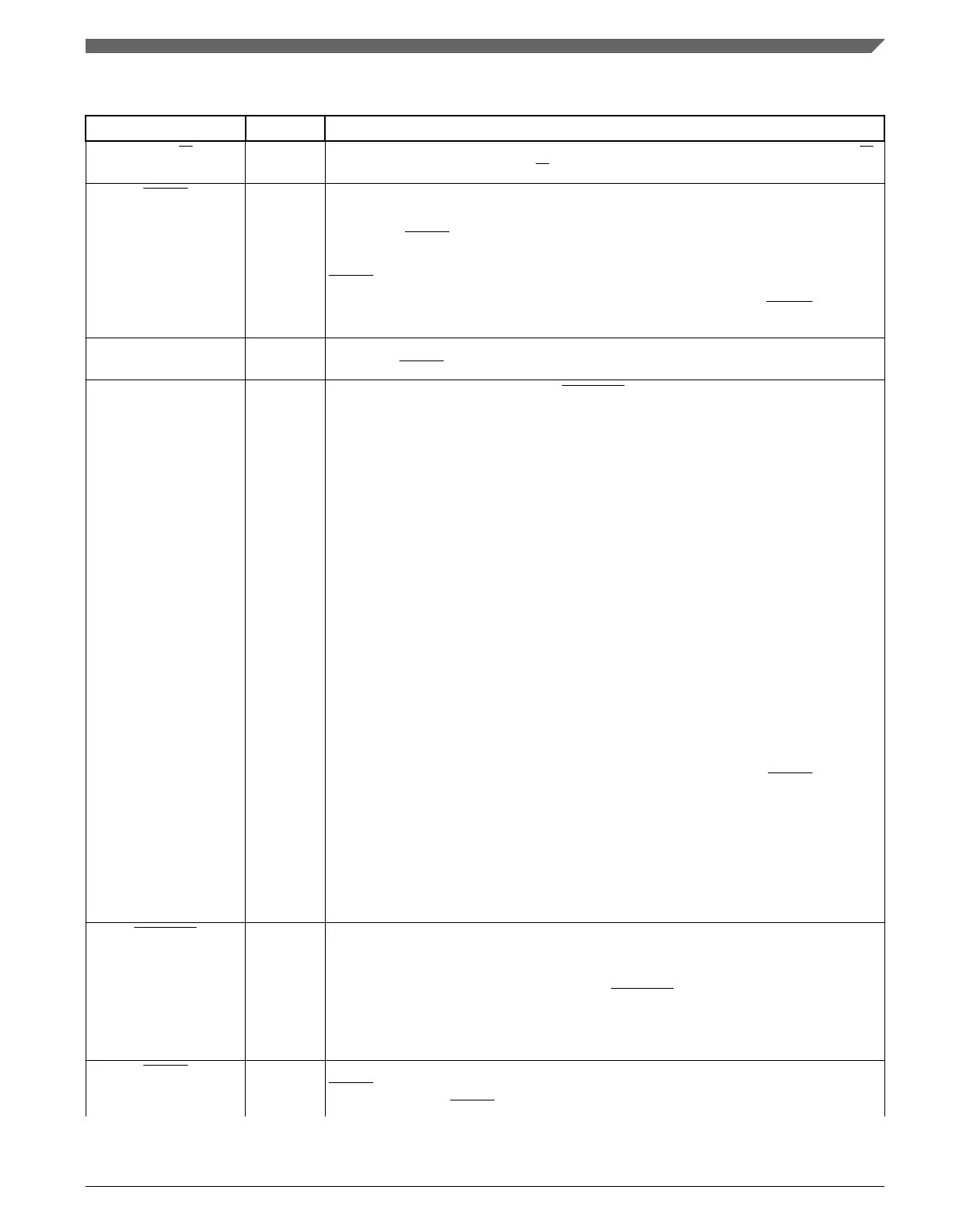

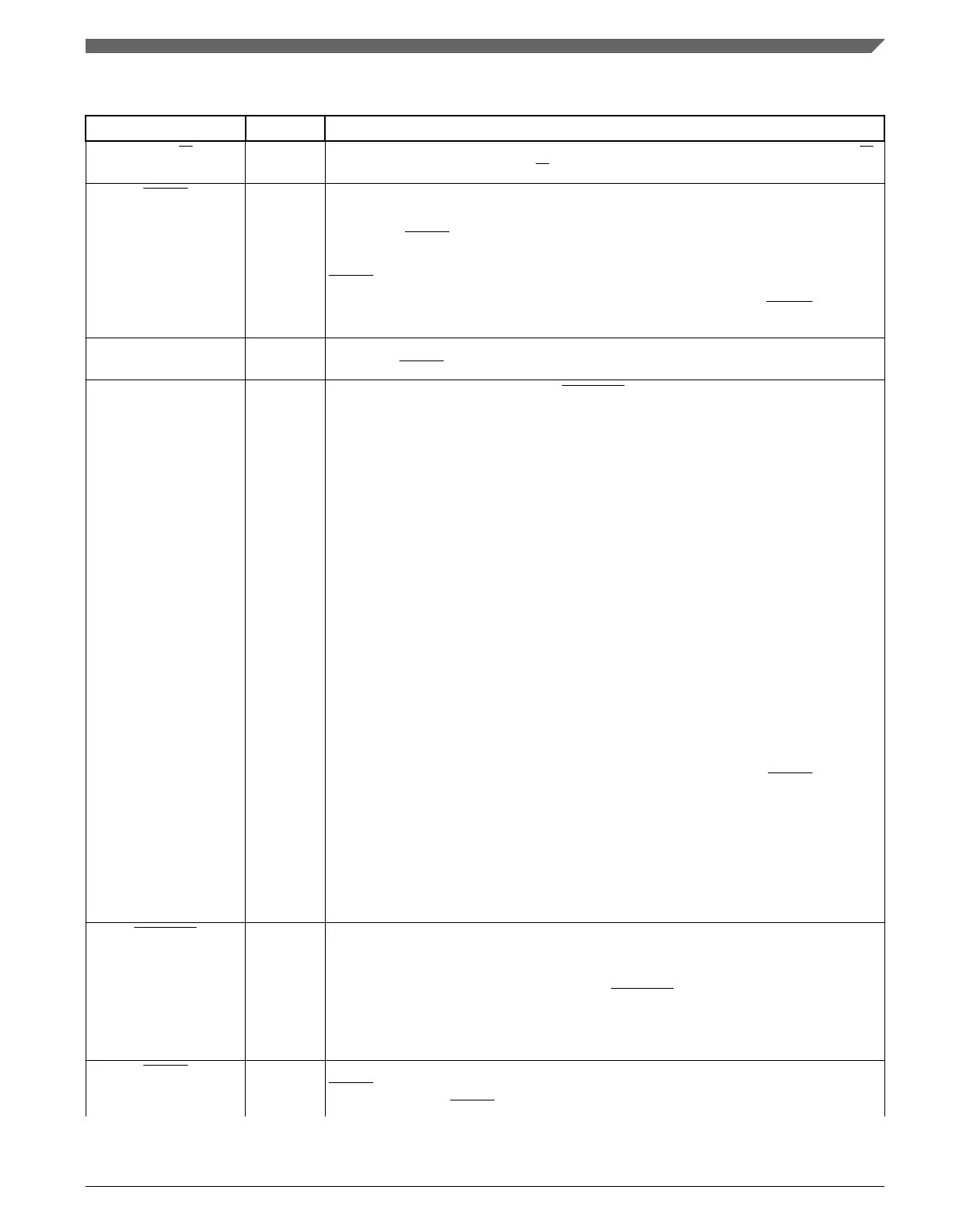

Table 31-1. FlexBus signal descriptions (continued)

Signal I/O Function

FB_R/W O Read/Write—Indicates whether the current bus operation is a read operation (FB_R/W

high) or a write operation (FB_R/W low).

FB_TS O Transfer Start—Indicates that the chip has begun a bus transaction and that the

address and attributes are valid.

An inverted FB_TS is available as an address latch enable (FB_ALE), which indicates

when the address is being driven on the FB_AD bus.

FB_TS/FB_ALE is asserted for one bus clock cycle.

The chip can extend this signal until the first positive clock edge after FB_CS asserts.

See CSCR[EXTS] and Extended Transfer Start/Address Latch Enable.

FB_ALE O Address Latch Enable—Indicates when the address is being driven on the FB_A bus

(inverse of FB_TS).

FB_TSIZ1–FB_TSIZ0 O Transfer Size—Indicates (along with FB_TBST) the data transfer size of the current

bus operation. The interface supports 8-, 16-, and 32-bit operand transfers and allows

accesses to 8-, 16-, and 32-bit data ports.

• 00b = 4 bytes

• 01b = 1 byte

• 10b = 2 bytes

• 11b = 16 bytes (line)

For misaligned transfers, FB_TSIZ1–FB_TSIZ0 indicate the size of each transfer. For

example, if a 32-bit access through a 32-bit port device occurs at a misaligned offset of

1h, 8 bits are transferred first (FB_TSIZ1–FB_TSIZ0 = 01b), 16 bits are transferred

next at offset 2h (FB_TSIZ1–FB_TSIZ0 = 10b), and the final 8 bits are transferred at

offset 4h (FB_TSIZ1–FB_TSIZ0 = 01b).

For aligned transfers larger than the port size, FB_TSIZ1–FB_TSIZ0 behave as follows:

• If bursting is used, FB_TSIZ1–FB_TSIZ0 are driven to the transfer size.

• If bursting is inhibited, FB_TSIZ1–FB_TSIZ0 first show the entire transfer size

and then show the port size.

For burst-inhibited transfers, FB_TSIZ1–FB_TSIZ0 change with each

FB_TS assertion

to reflect the next transfer size.

For transfers to port sizes smaller than the transfer size, FB_TSIZ1–FB_TSIZ0 indicate

the size of the entire transfer on the first access and the size of the current port transfer

on subsequent transfers. For example, for a 32-bit write to an 8-bit port, FB_TSIZ1–

FB_TSIZ0 are 00b for the first transaction and 01b for the next three transactions. If

bursting is used for a 32-bit write to an 8-bit port, FB_TSIZ1–FB_TSIZ0 are driven to

00b for the entire transfer.

FB_TBST

O Transfer Burst—Indicates that a burst transfer is in progress as driven by the chip. A

burst transfer can be 2 to 16 beats depending on FB_TSIZ1–FB_TSIZ0 and the port

size.

Note:

When a burst transfer is in progress (FB_TBST = 0b), the transfer size is 16

bytes (FB_TSIZ1–FB_TSIZ0 = 11b), and the address is misaligned within the

16-byte boundary, the external memory or peripheral must be able to wrap

around the address.

FB_TA I Transfer Acknowledge—Indicates that the external data transfer is complete. When

FB_TA is asserted during a read transfer, FlexBus latches the data and then terminates

the transfer. When FB_TA is asserted during a write transfer, the transfer is terminated.

Table continues on the next page...

Chapter 31 External Bus Interface (FlexBus)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 695

Loading...

Loading...