UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 16 of 841

NXP Semiconductors

UM10360

Chapter 2: LPC176x/5x Memory map

2.4 Memory re-mapping

The Cortex-M3 incorporates a mechanism that allows remapping the interrupt vector table

to alternate locations in the memory map. This is controlled via the Vector Table Offset

Register contained in the Cortex-M3. Refer to Section 6.4

and Section 34.4.3.5 of the

Cortex-M3 User Guide appended to this manual for details of the Vector Table Offset

feature.

Boot ROM re-mapping

Following a hardware reset, the Boot ROM is temporarily mapped to address 0. This is

normally transparent to the user. However, if execution is halted immediately after reset by

a debugger, it should correct the mapping for the user. See Section 33.6

.

2.5 AHB arbitration

The Multilayer AHB Matrix arbitrates between several masters. By default, the Cortex-M3

D-code bus has the highest priority, followed by the I-Code bus. All other masters share a

lower priority.

2.6 Bus fault exceptions

The LPC176x/5x generates Bus Fault exception if an access is attempted for an address

that is in a reserved or unassigned address region. The regions are areas of the memory

map that are not implemented for a specific derivative. These include all spaces marked

“reserved” in Figure 3

.

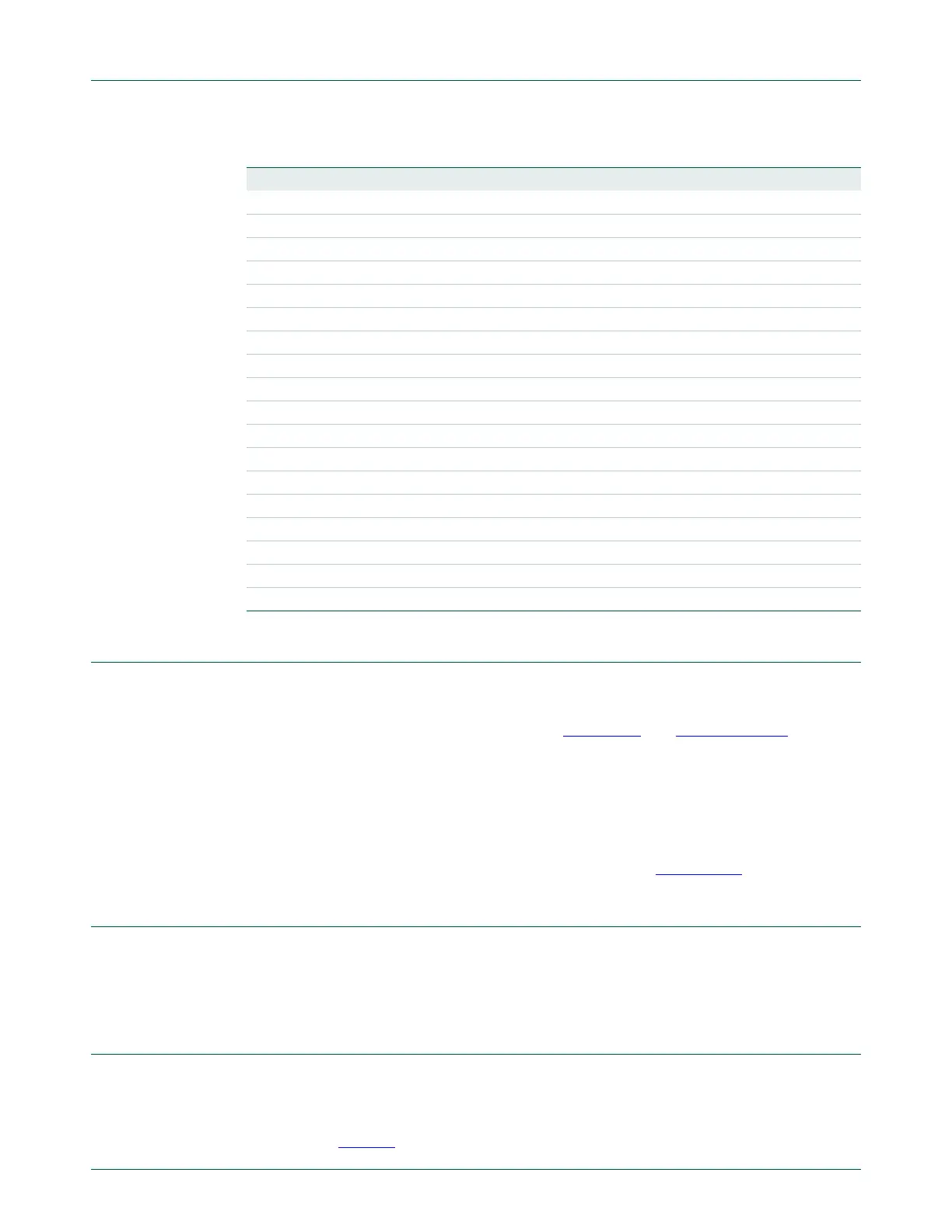

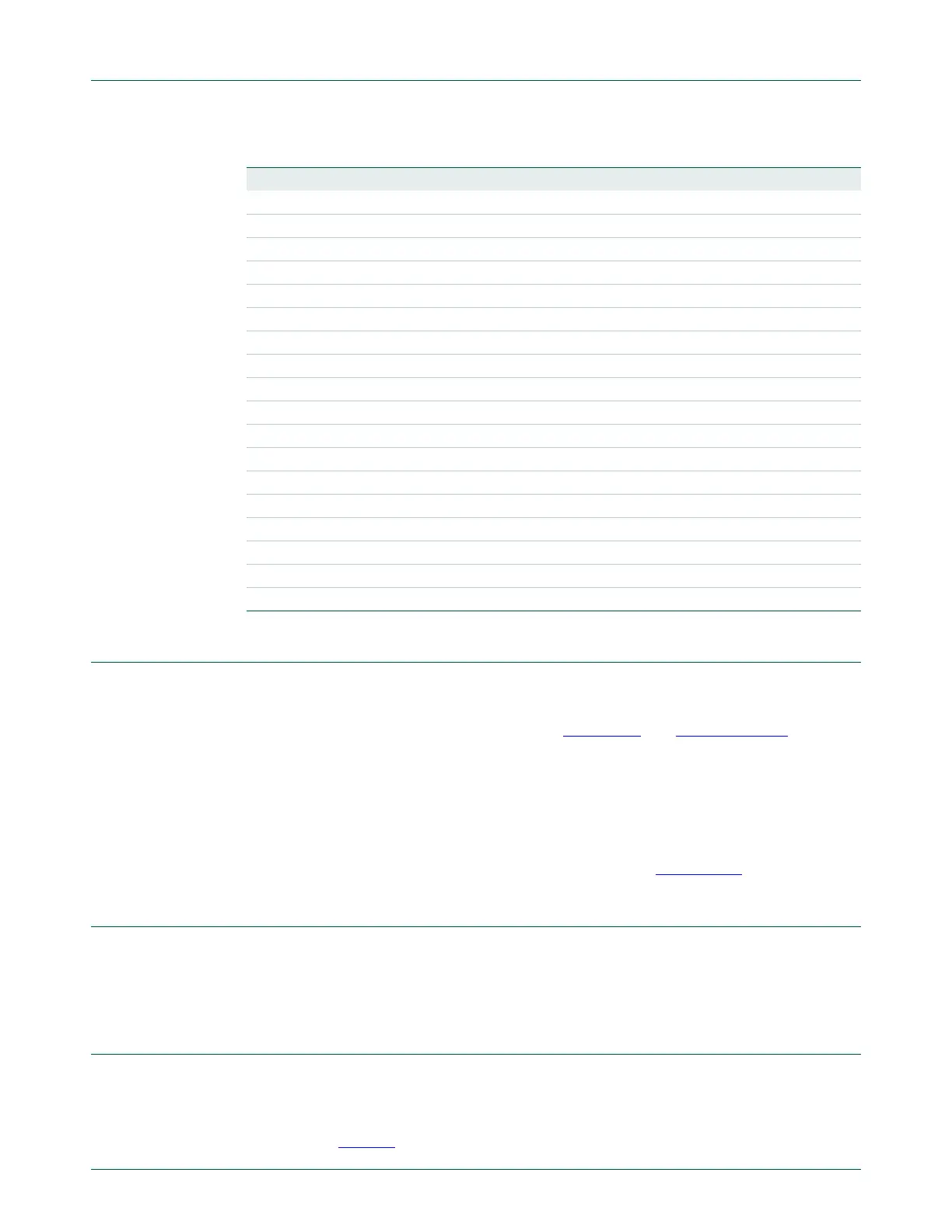

Table 5. APB1 peripherals and base addresses

APB1 peripheral Base address Peripheral name

0 0x4008 0000 reserved

1 0x4008 4000 reserved

2 0x4008 8000 SSP0

3 0x4008 C000 DAC

4 0x4009 0000 Timer 2

5 0x4009 4000 Timer 3

6 0x4009 8000 UART2

7 0x4009 C000 UART3

8 0x400A 0000 I

2

C2

9 0x400A 4000 reserved

10 0x400A 8000 I

2

S

11 0x400A C000 reserved

12 0x400B 0000 Repetitive interrupt timer

13 0x400B 4000 reserved

14 0x400B 8000 Motor control PWM

15 0x400B C000 Quadrature Encoder Interface

16 to 30 0x400C 0000 to 0x400F 8000 reserved

31 0x400F C000 System control

Loading...

Loading...