UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 565 of 841

NXP Semiconductors

UM10360

Chapter 27: LPC176x/5x Real-Time Clock (RTC) and backup registers

27.6.2.5 RTC Auxiliary control register (RTC_AUX - 0x4002 405C)

The RTC Auxiliary Control register contains added interrupt flags for functions that are not

part of the Real Time Clock itself (the part recording the passage of time and generating

other time related functions). On the LPC176x/5x, the only added interrupt flag is for

failure of the RTC oscillator.

27.6.2.6 RTC Auxiliary Enable register (RTC_AUXEN - 0x4002 4058)

The RTC Auxiliary Enable Register controls whether additional interrupt sources

represented in the RTC Auxiliary control register are enabled.

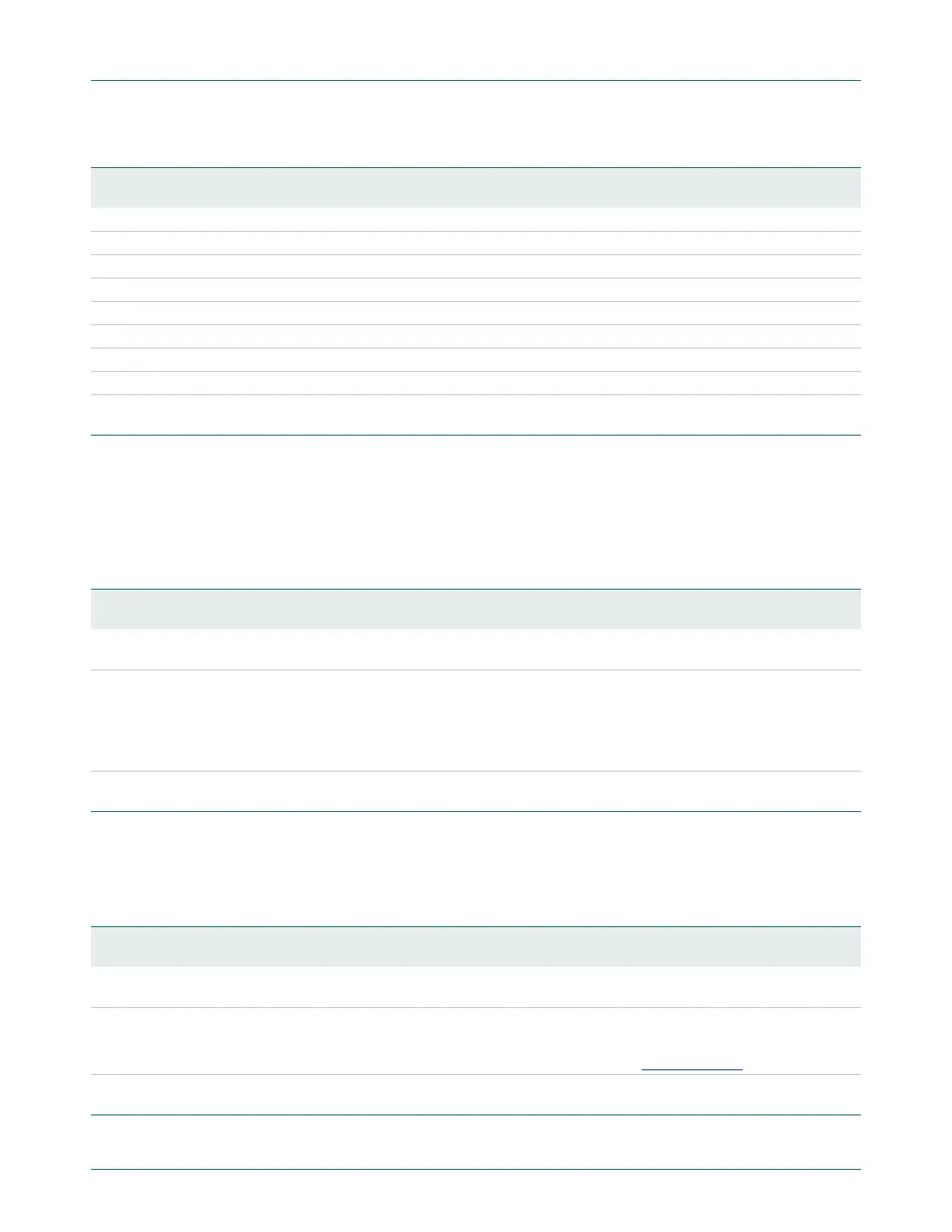

Table 511. Alarm Mask Register (AMR - address 0x4002 4010) bit description

Bit Symbol Description Reset

value

0 AMRSEC When 1, the Second value is not compared for the alarm. 0

1 AMRMIN When 1, the Minutes value is not compared for the alarm. 0

2 AMRHOUR When 1, the Hour value is not compared for the alarm. 0

3 AMRDOM When 1, the Day of Month value is not compared for the alarm. 0

4 AMRDOW When 1, the Day of Week value is not compared for the alarm. 0

5 AMRDOY When 1, the Day of Year value is not compared for the alarm. 0

6 AMRMON When 1, the Month value is not compared for the alarm. 0

7 AMRYEAR When 1, the Year value is not compared for the alarm. 0

31:8 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

Table 512. RTC Auxiliary control register (RTC_AUX - address 0x4002 405C) bit description

Bit Symbol Description Reset

value

3:0 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

4 RTC_OSCF RTC Oscillator Fail detect flag.

Read: this bit is set if the RTC oscillator stops, and when RTC power is first turned on. An

interrupt will occur when this bit is set, the RTC_OSCFEN bit in RTC_AUXEN is a 1, and the

RTC interrupt is enabled in the NVIC.

Write: writing a 1 to this bit clears the flag.

1

31:5 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

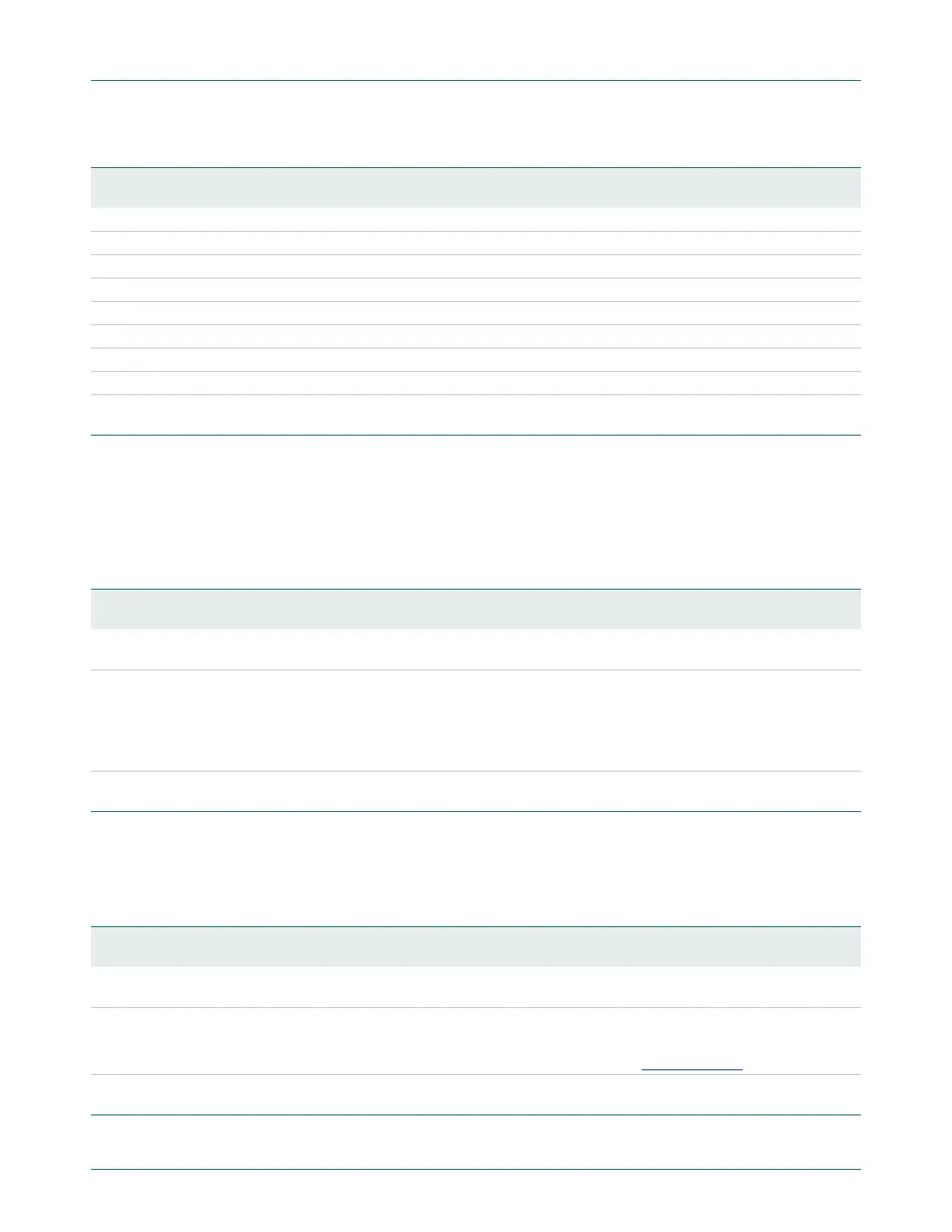

Table 513. RTC Auxiliary Enable register (RTC_AUXEN - address 0x4002 4058) bit description

Bit Symbol Description Reset

value

3:0 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

4 RTC_OSCFEN Oscillator Fail Detect interrupt enable.

When 0: the RTC Oscillator Fail detect interrupt is disabled.

When 1: the RTC Oscillator Fail detect interrupt is enabled. See Section 27.6.2.5

.

0

31:5 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

Loading...

Loading...