UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 516 of 841

NXP Semiconductors

UM10360

Chapter 24: LPC176x/5x Pulse Width Modulator (PWM)

[1] Reset Value reflects the data stored in used bits only. It does not include reserved bits content.

24.6.1 PWM Interrupt Register (PWM1IR - 0x4001 8000)

The PWM Interrupt Register consists of 11 bits (Table 446), 7 for the match interrupts and

4 reserved for the future use. If an interrupt is generated then the corresponding bit in the

PWMIR will be high. Otherwise, the bit will be low. Writing a logic 1 to the corresponding

IR bit will reset the interrupt. Writing a 0 has no effect.

CR2 Capture Register 2. See CR0 description. RO 0 PWM1CR2 -

0x4001 8034

CR3 Capture Register 3. See CR0 description. RO 0 PWM1CR3 -

0x4001 8038

MR4 Match Register 4. MR4 can be enabled in the MCR to reset the TC, stop

both the TC and PC, and/or generate an interrupt when it matches the TC.

In addition, a match between this value and the TC clears PWM4 in either

edge mode, and sets PWM5 if it’s in double-edge mode.

R/W 0 PWM1MR4 -

0x4001 8040

MR5 Match Register 5. MR5 can be enabled in the MCR to reset the TC, stop

both the TC and PC, and/or generate an interrupt when it matches the TC.

In addition, a match between this value and the TC clears PWM5 in either

edge mode, and sets PWM6 if it’s in double-edge mode.

R/W 0 PWM1MR5 -

0x4001 8044

MR6 Match Register 6. MR6 can be enabled in the MCR to reset the TC, stop

both the TC and PC, and/or generate an interrupt when it matches the TC.

In addition, a match between this value and the TC clears PWM6 in either

edge mode.

R/W 0 PWM1MR6 -

0x4001 8048

PCR PWM Control Register. Enables PWM outputs and selects PWM channel

types as either single edge or double edge controlled.

R/W 0 PWM1PCR -

0x4001 804C

LER Load Enable Register. Enables use of new PWM match values. R/W 0 PWM1LER -

0x4001 8050

CTCR Count Control Register. The CTCR selects between Timer and Counter

mode, and in Counter mode selects the signal and edge(s) for counting.

R/W 0 PWM1CTCR -

0x4001 8070

Table 445. PWM1 register map …continued

Generic

Name

Description Access Reset

Value

[1]

PWMn Register

Name & Address

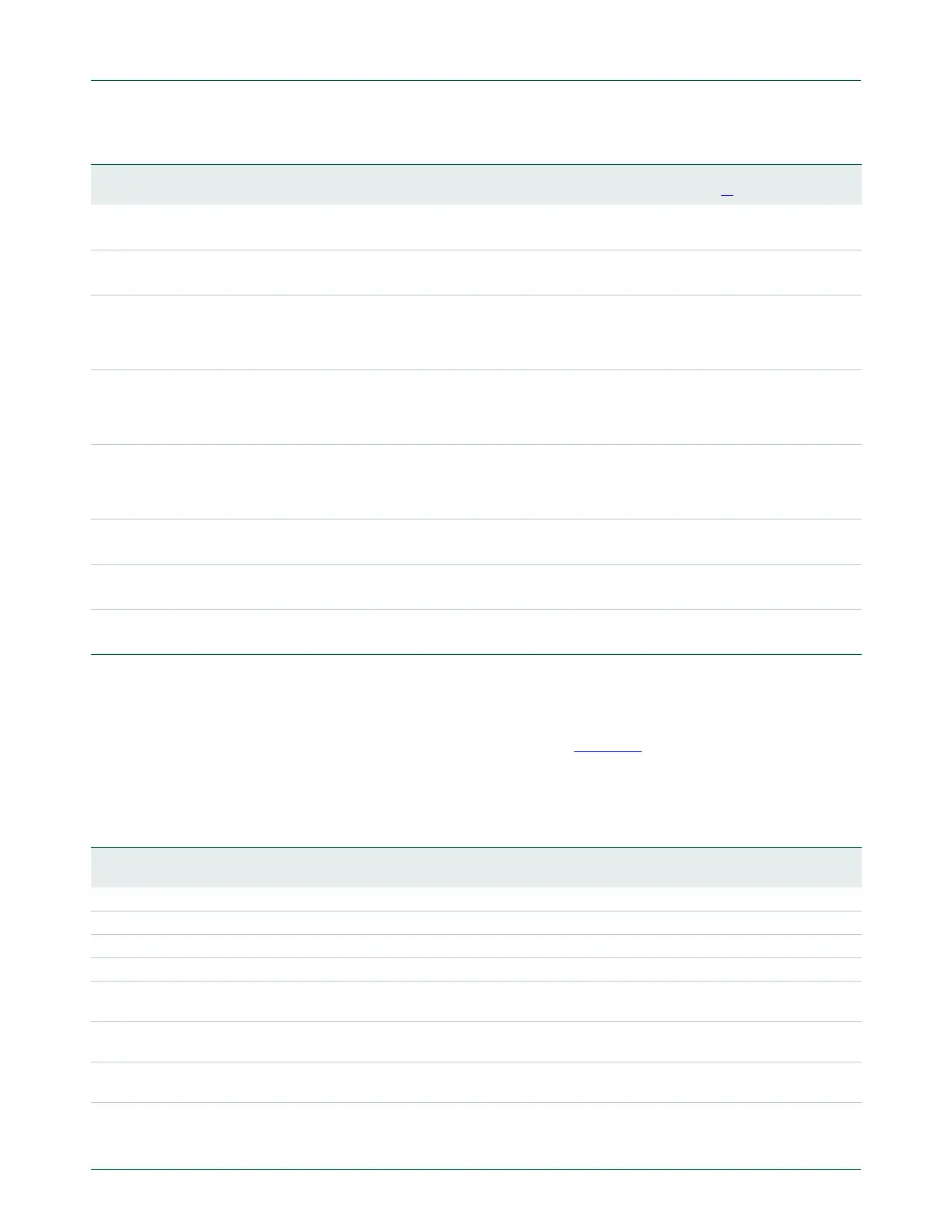

Table 446: PWM Interrupt Register (PWM1IR - address 0x4001 8000) bit description

Bit Symbol Description Reset

Value

0 PWMMR0 Interrupt Interrupt flag for PWM match channel 0. 0

1 PWMMR1 Interrupt Interrupt flag for PWM match channel 1. 0

2 PWMMR2 Interrupt Interrupt flag for PWM match channel 2. 0

3 PWMMR3 Interrupt Interrupt flag for PWM match channel 3. 0

4 PWMCAP0

Interrupt

Interrupt flag for capture input 0 0

5 PWMCAP1

Interrupt

Interrupt flag for capture input 1. 0

7:6 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

8 PWMMR4 Interrupt Interrupt flag for PWM match channel 4. 0

Loading...

Loading...