UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 551 of 841

NXP Semiconductors

UM10360

Chapter 26: LPC176x/5x Quadrature Encoder Interface (QEI)

26.6.2 Control registers

26.6.2.1 QEI Control register (QEICON - 0x400B C000)

This register contains bits which control the operation of the position and velocity counters

of the QEI module.

26.6.2.2 QEI Configuration register (QEICONF - 0x400B C008)

This register contains the configuration of the QEI module.

26.6.2.3 QEI Status register (QEISTAT - 0x400B C004)

This register provides the status of the encoder interface.

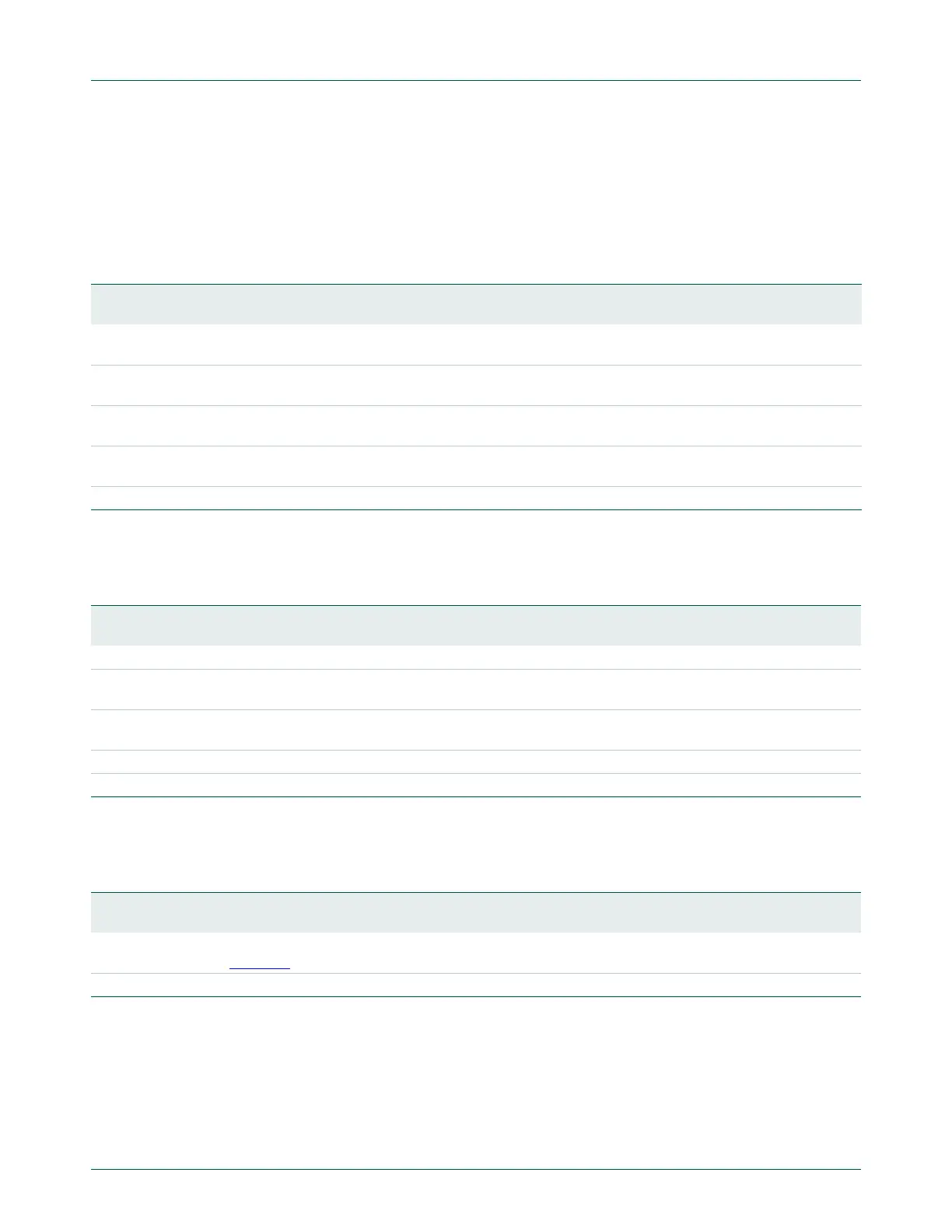

Table 484: QEI Control register (QEICON - address 0x400B C000) bit description

Bit Symbol Description Reset

value

0 RESP Reset position counter. When set = 1, resets the position counter to all zeros. Autoclears when

the position counter is cleared.

0

1 RESPI Reset position counter on index. When set = 1, resets the position counter to all zeros when an

index pulse occurs. Autoclears when the position counter is cleared.

0

2 RESV Reset velocity. When set = 1, resets the velocity counter to all zeros and reloads the velocity

timer. Autoclears when the velocity counter is cleared.

0

3 RESI Reset index counter. When set = 1, resets the index counter to all zeros. Autoclears when the

index counter is cleared.

0

31:4 - reserved 0

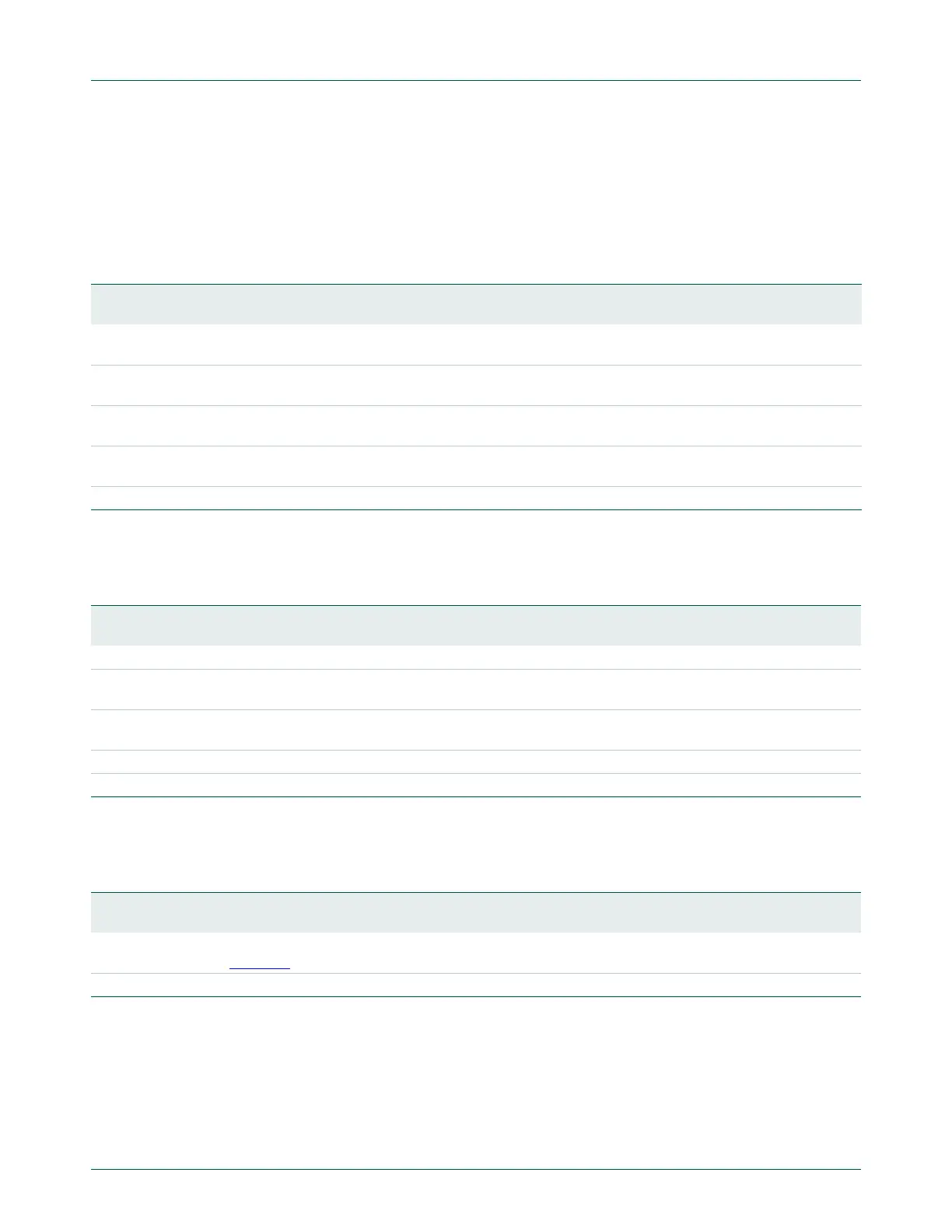

Table 485: QEI Configuration register (QEICONF - address 0x400B C008) bit description

Bit Symbol Description Reset

value

0 DIRINV Direction invert. When = 1, complements the DIR bit. 0

1 SIGMODE Signal Mode. When = 0, PhA and PhB function as quadrature encoder inputs. When = 1, PhA

functions as the direction signal and PhB functions as the clock signal.

0

2 CAPMODE Capture Mode. When = 0, only PhA edges are counted (2X). When = 1, BOTH PhA and PhB

edges are counted (4X), increasing resolution but decreasing range.

0

3 INVINX Invert Index. When set, inverts the sense of the index input. 0

31:4 - reserved 0

Table 486: QEI Interrupt Status register (QEISTAT - address 0x400B C004) bit description

Bit Symbol Description Reset

value

0 DIR Direction bit. In combination with DIRINV bit indicates forward or reverse direction. See

Table 481

.

31:1 - reserved 0

Loading...

Loading...