UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 160 of 841

NXP Semiconductors

UM10360

Chapter 10: LPC176x/5x Ethernet

• It is enabled and the Rx/TxEnable bit is set in the Command register or it just got

disabled while still transmitting or receiving a frame.

• Also, for the transmit channel, the transmit queue is not empty

i.e. ProduceIndex != ConsumeIndex.

• Also, for the receive channel, the receive queue is not full

i.e. ProduceIndex != ConsumeIndex - 1.

The status transitions from active to inactive if the channel is disabled by a software reset

of the Rx/TxEnable bit in the Command register and the channel has committed the status

and data of the current frame to memory. The status also transitions to inactive if the

transmit queue is empty or if the receive queue is full and status and data have been

committed to memory.

10.12.3 Receive Descriptor Base Address Register (RxDescriptor -

0x5000 0108)

The Receive Descriptor base address register (RxDescriptor) has an address of

0x5000 0108. Its bit definition is shown in Table 150

.

The receive descriptor base address is a byte address aligned to a word boundary i.e.

LSB 1:0 are fixed to “00”. The register contains the lowest address in the array of

descriptors.

10.12.4 Receive Status Base Address Register (RxStatus - 0x5000 010C)

The receive descriptor base address is a byte address aligned to a word boundary i.e.

LSB 1:0 are fixed to “00”. The register contains the lowest address in the array of

descriptors.

The receive status base address is a byte address aligned to a double word boundary i.e.

LSB 2:0 are fixed to “000”.

10.12.5 Receive Number of Descriptors Register (RxDescriptor - 0x5000 0110)

The Receive Number of Descriptors register (RxDescriptorNumber) has an address of

0x5000 0110. Its bit definition is shown in Table 152

.

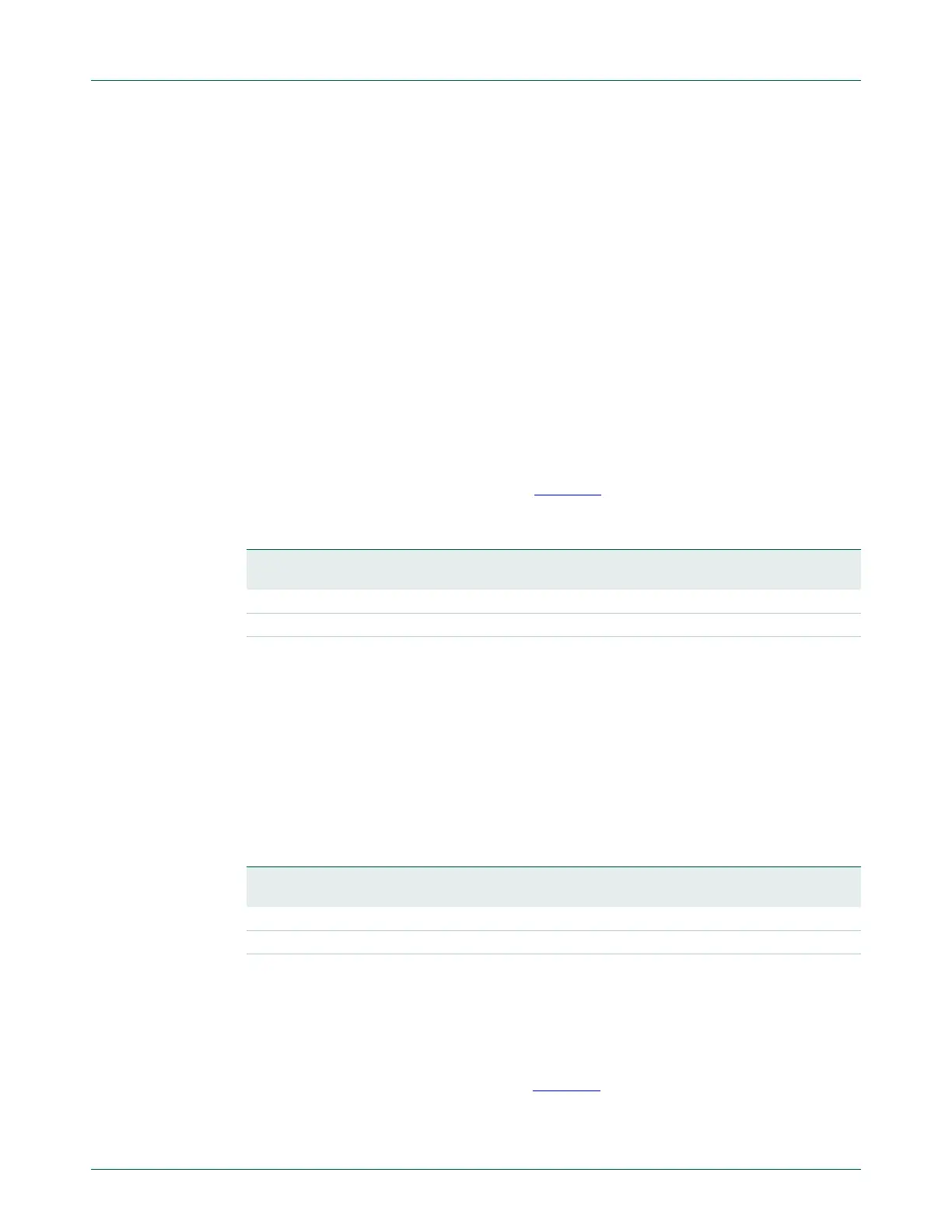

Table 150. Receive Descriptor Base Address register (RxDescriptor - address 0x5000 0108)

bit description

Bit Symbol Function Reset

value

1:0 - Fixed to ’00’ -

31:2 RxDescriptor MSBs of receive descriptor base address. 0x0

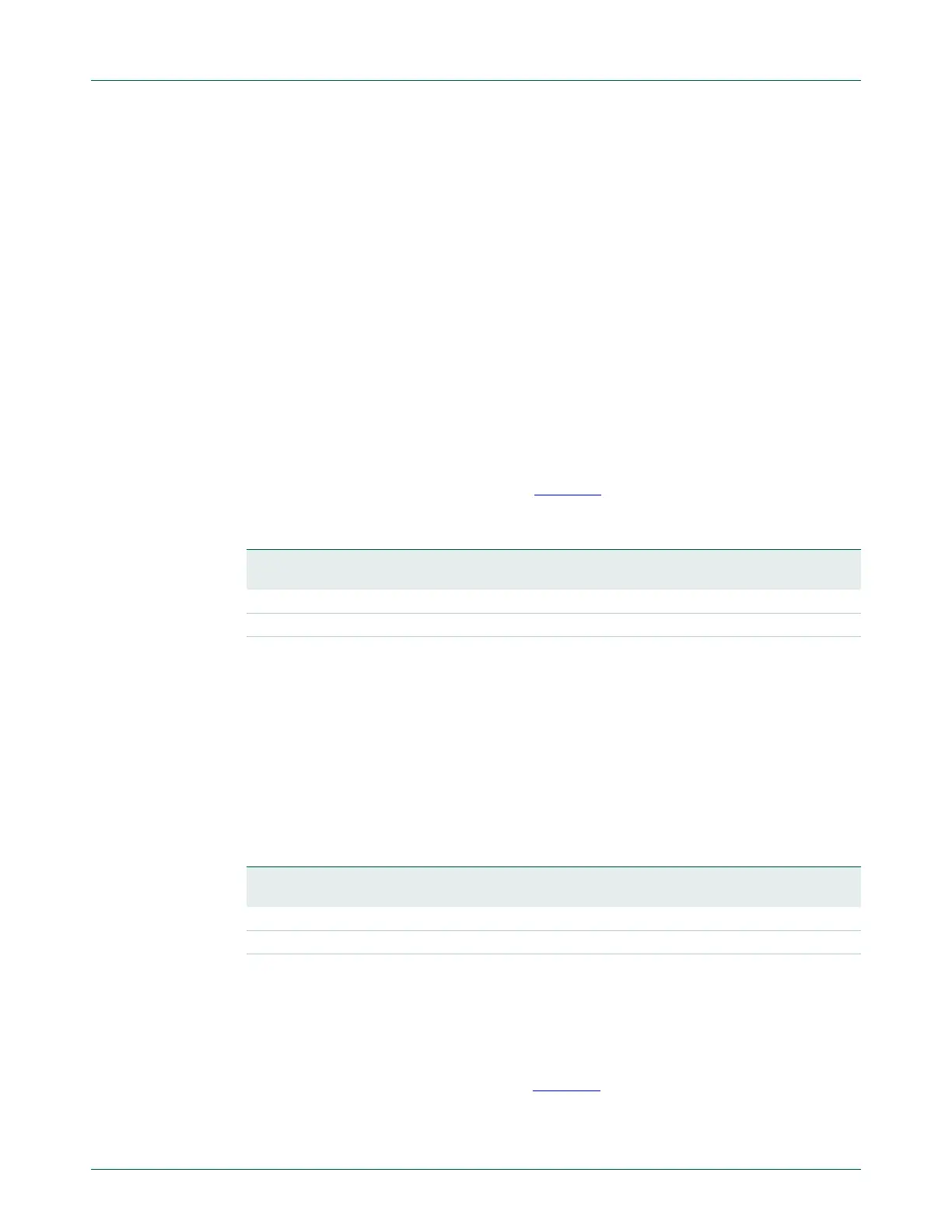

Table 151. receive Status Base Address register (RxStatus - address 0x5000 010C) bit

description

Bit Symbol Function Reset

value

2:0 - Fixed to ’000’ -

31:3 RxStatus MSBs of receive status base address. 0x0

Loading...

Loading...