UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 530 of 841

NXP Semiconductors

UM10360

Chapter 25: LPC176x/5x Motor control PWM

25.7.2.2 MCPWM Capture Control set address (MCCAPCON_SET - 0x400B 8010)

Writing ones to this write-only address sets the corresponding bits in MCCAPCON.

25.7.2.3 MCPWM Capture control clear address (MCCAPCON_CLR - 0x400B 8014)

Writing ones to this write-only address clears the corresponding bits in MCCAPCON.

25.7.3 MCPWM Interrupt registers

The Motor Control PWM module includes the following interrupt sources:

All MCPWM interrupt registers contain one bit for each source as shown in Table 462.

7.3.1 MCPWM Interrupt Enable read address (MCINTEN - 0x400B 8050)

The MCINTEN register controls which of the MCPWM interrupts are enabled. This

address is read-only, but the underlying register can be modified by writing to addresses

MCINTEN_SET and MCINTEN_CLR.

Table 459. MCPWM Capture Control set address (MCCAPCON_SET - 0x400B 8010) bit description

Bit Description

31:0 Writing ones to this address sets the corresponding bits in the MCCAPCON register. See Table 458.

Table 460. MCPWM Capture control clear register (MCCAPCON_CLR - address 0x400B 8014) bit description

Bit Description

31:0 Writing ones to this address clears the corresponding bits in the MCCAPCON register. See Table 458.

Table 461. Motor Control PWM interrupts

Symbol Description

ILIM0/1/2 Limit interrupts for channels 0, 1, 2.

IMAT0/1/2 Match interrupts for channels 0, 1, 2.

ICAP0/1/2 Capture interrupts for channels 0, 1, 2.

ABORT Fast abort interrupt

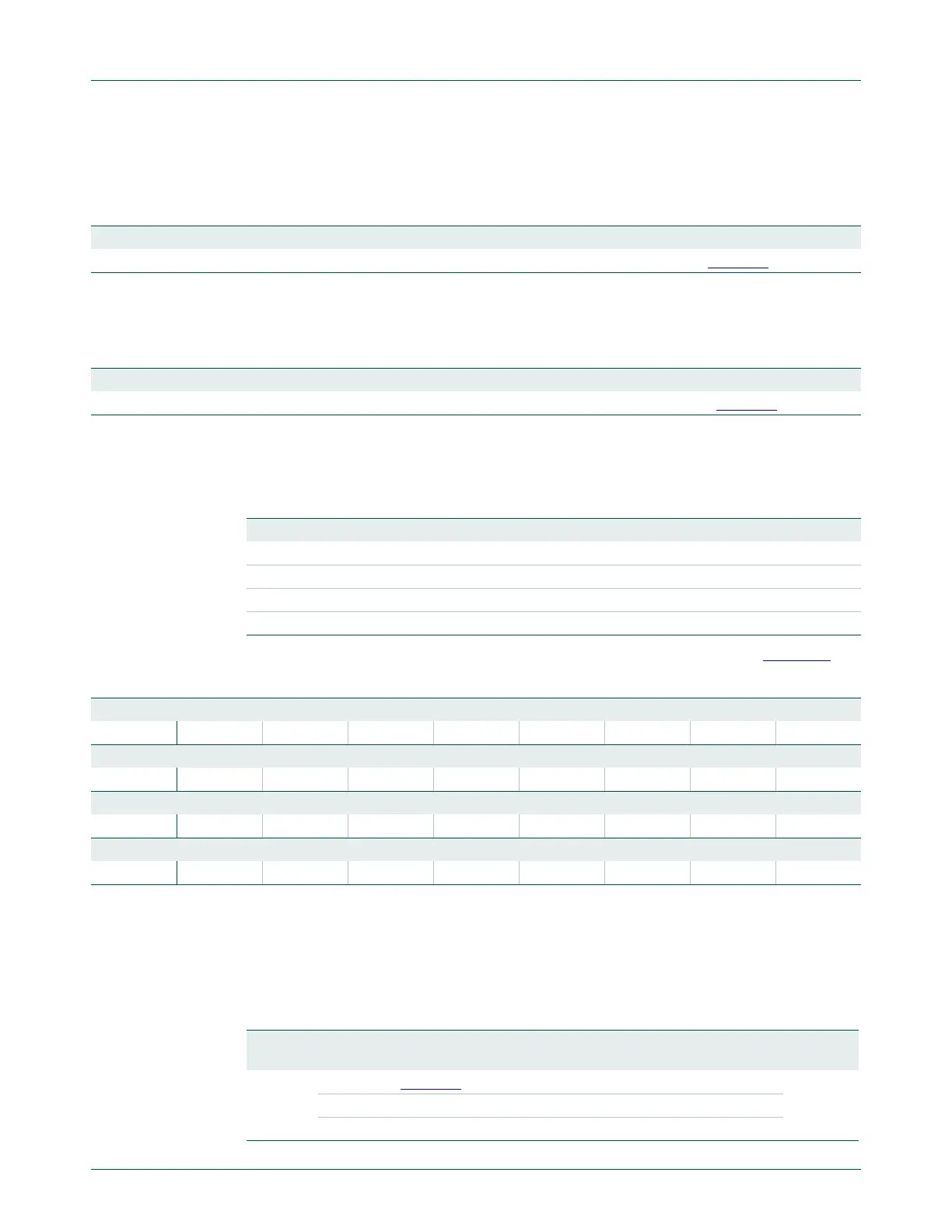

Table 462. Interrupt sources bit allocation table

Bit 31 30 29 28 27 26 25 24

Symbol

--------

Bit 23 22 21 20 19 18 17 16

Symbol

--------

Bit 15 14 13 12 11 10 9 8

Symbol

ABORT - - - - ICAP2 IMAT2 ILIM2

Bit 7 6 5 4 3 2 1 0

Symbol

- ICAP1 IMAT1 ILIM1 - ICAP0 IMAT0 ILIM0

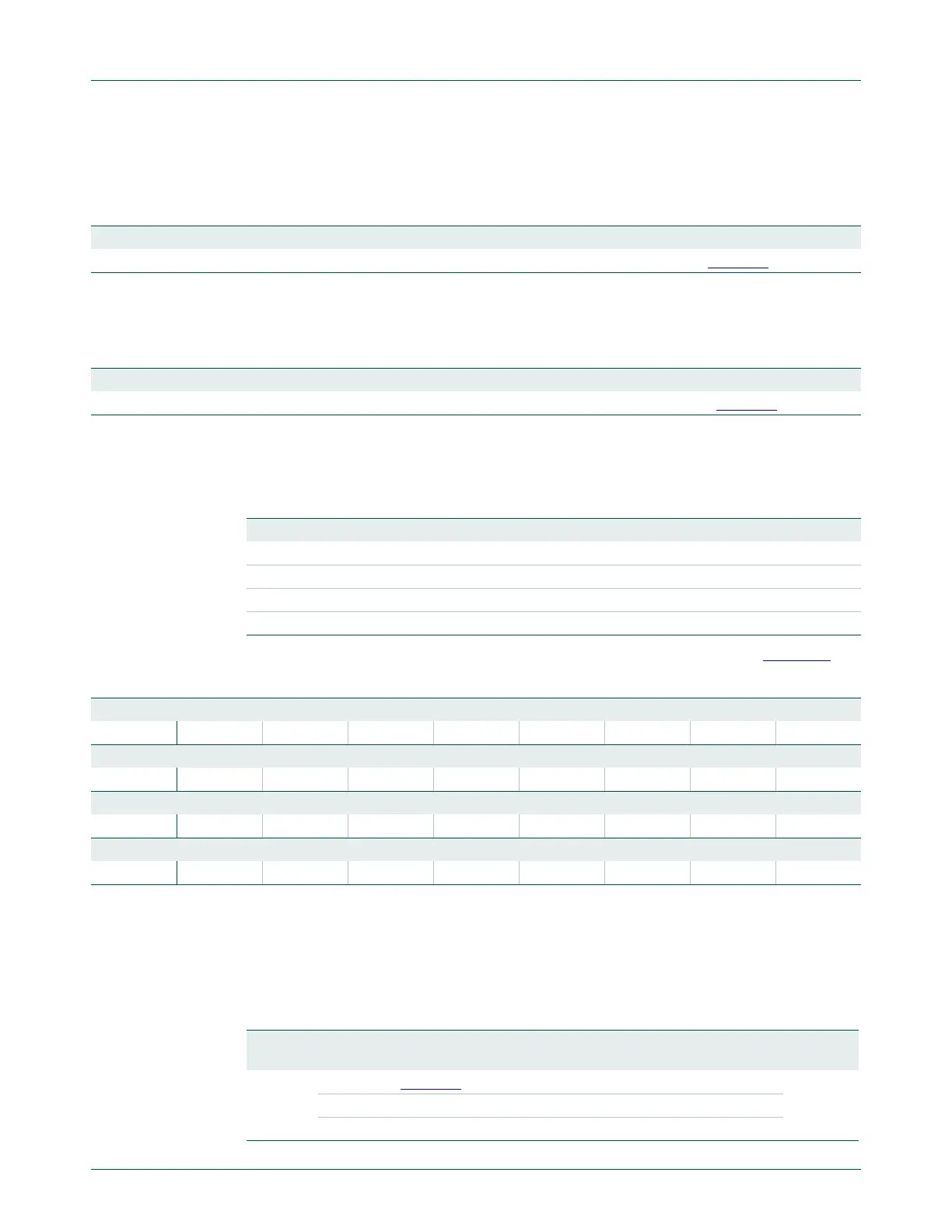

Table 463. MCPWM Interrupt Enable read address (MCINTEN - 0x400B 8050) bit description

Bit Value Description Reset

value

31:0 See Table 462 for the bit allocation. 0

1 Interrupt enabled.

0 Interrupt disabled.

Loading...

Loading...