UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 324 of 841

NXP Semiconductors

UM10360

Chapter 15: LPC176x/5x UART1

15.4.5 UART1 Interrupt Identification Register (U1IIR - 0x4001 0008)

The U1IIR provides a status code that denotes the priority and source of a pending

interrupt. The interrupts are frozen during an U1IIR access. If an interrupt occurs during

an U1IIR access, the interrupt is recorded for the next U1IIR access.

Bit U1IIR[9:8] are set by the auto-baud function and signal a time-out or end of auto-baud

condition. The auto-baud interrupt conditions are cleared by setting the corresponding

Clear bits in the Auto-baud Control Register.

If the IntStatus bit is 1 no interrupt is pending and the IntId bits will be zero. If the IntStatus

is 0, a non auto-baud interrupt is pending in which case the IntId bits identify the type of

interrupt and handling as described in Table 296

. Given the status of U1IIR[3:0], an

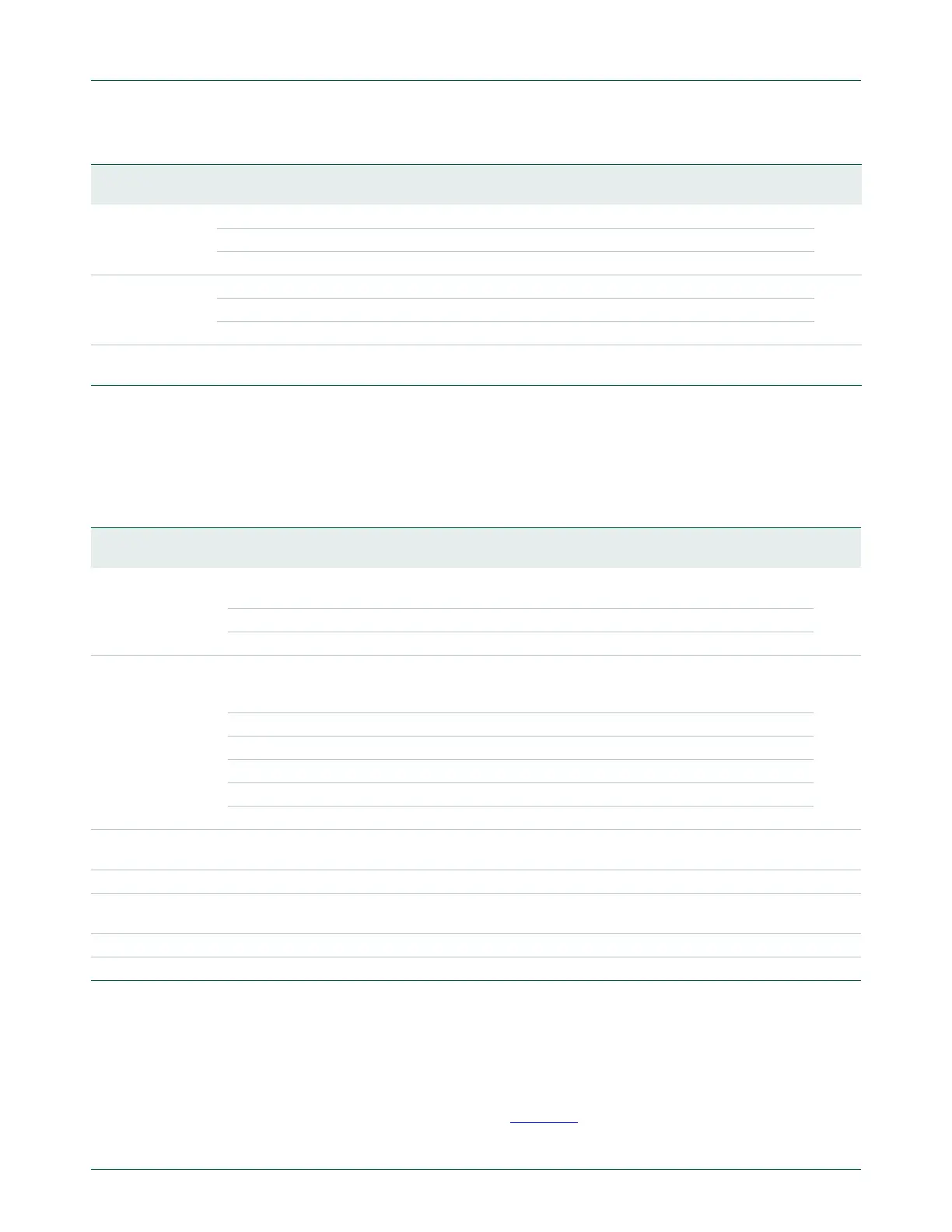

8 ABEOIntEn Enables the end of auto-baud interrupt. 0

0 Disable end of auto-baud Interrupt.

1 Enable end of auto-baud Interrupt.

9 ABTOIntEn Enables the auto-baud time-out interrupt. 0

0 Disable auto-baud time-out Interrupt.

1 Enable auto-baud time-out Interrupt.

31:10 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

Table 294: UART1 Interrupt Enable Register (U1IER - address 0x4001 0004 when DLAB = 0) bit description …continued

Bit Symbol Value Description Reset

Value

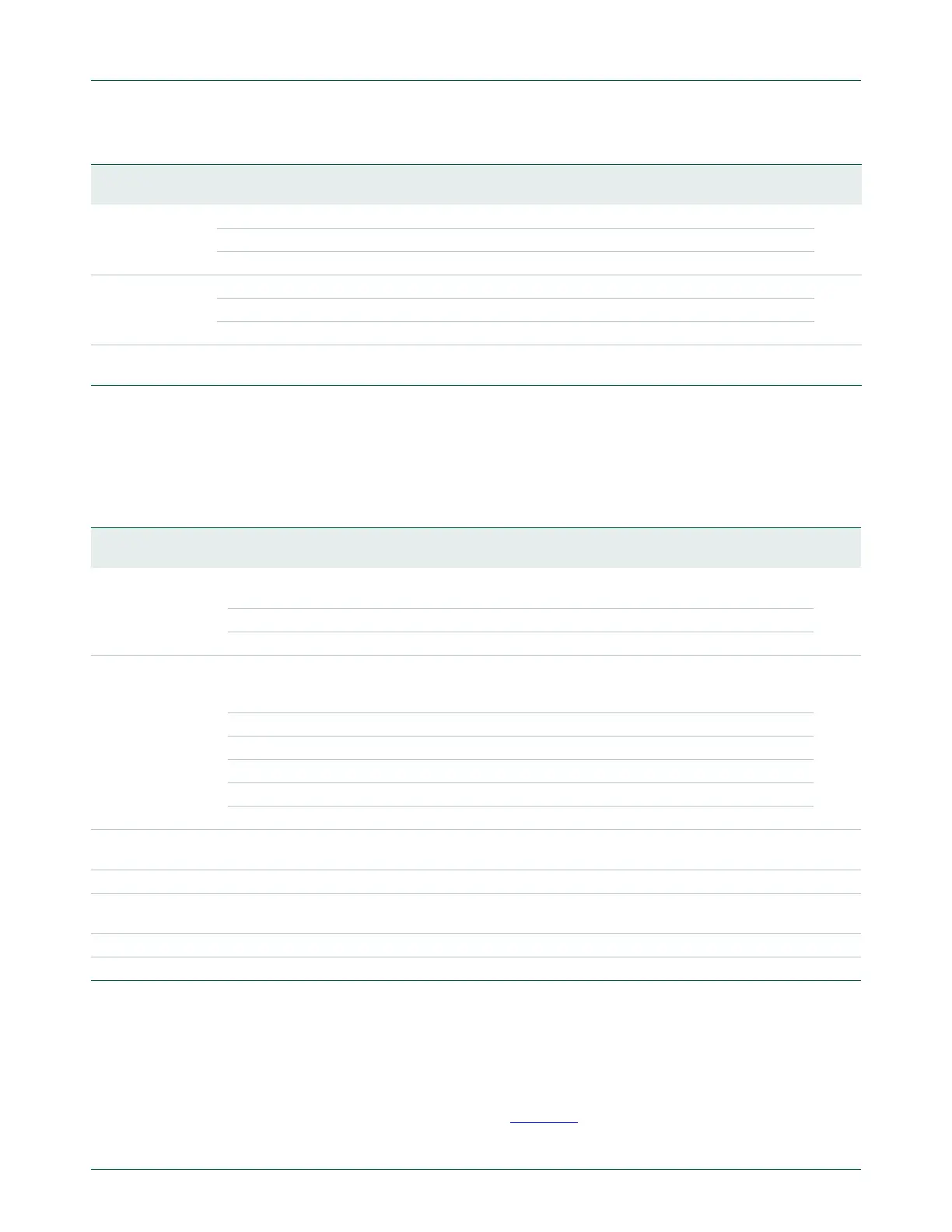

Table 295: UART1 Interrupt Identification Register (U1IIR - address 0x4001 0008) bit description

Bit Symbol Value Description Reset

Value

0 IntStatus Interrupt status. Note that U1IIR[0] is active low. The pending interrupt can be

determined by evaluating U1IIR[3:1].

1

0 At least one interrupt is pending.

1 No interrupt is pending.

3:1 IntId Interrupt identification. U1IER[3:1] identifies an interrupt corresponding to the UART1

Rx or TX FIFO. All other combinations of U1IER[3:1] not listed below are reserved

(100,101,111).

0

011 1 - Receive Line Status (RLS).

010 2a - Receive Data Available (RDA).

110 2b - Character Time-out Indicator (CTI).

001 3 - THRE Interrupt.

000 4 - Modem Interrupt.

5:4 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

7:6 FIFO Enable Copies of U1FCR[0]. 0

8 ABEOInt End of auto-baud interrupt. True if auto-baud has finished successfully and interrupt is

enabled.

0

9 ABTOInt Auto-baud time-out interrupt. True if auto-baud has timed out and interrupt is enabled. 0

31:10 - Reserved, the value read from a reserved bit is not defined. NA

Loading...

Loading...