UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 20 December 2013 657 of 841

NXP Semiconductors

UM10360

Chapter 34: Appendix: Cortex-M3 user guide

• If n is 32, then the value of the result is same as the value in Rm, and if the carry flag

is updated, it is updated to bit[31] of Rm.

•

ROR

with shift length, n, more than 32 is the same as

ROR

with shift length n-32.

34.2.3.4.5 RRX

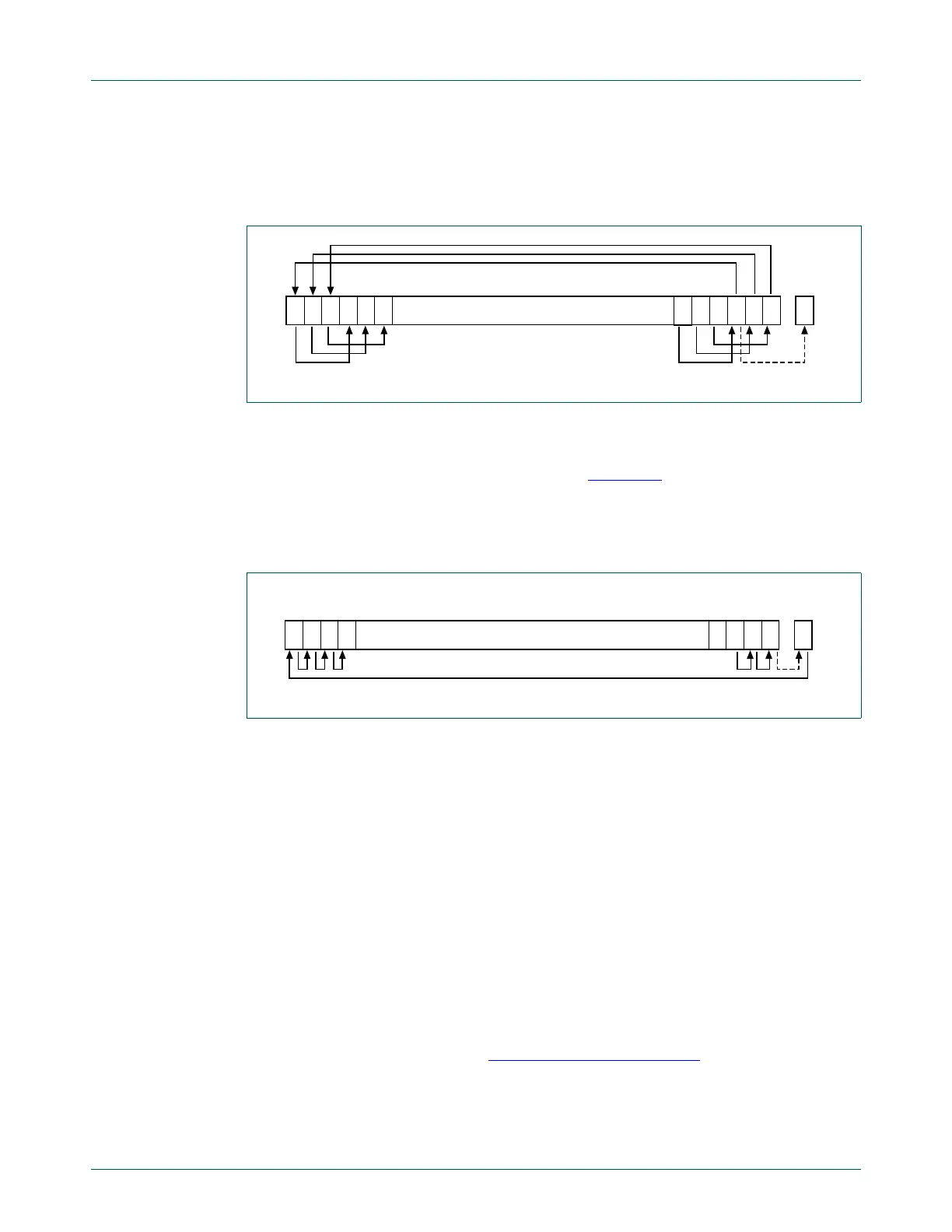

Rotate right with extend moves the bits of the register Rm to the right by one bit. And it

copies the carry flag into bit[31] of the result. See Figure 145

.

When the instruction is

RRXS

or when RRX is used in Operand2 with the instructions

MOVS

,

MVNS

,

ANDS

,

ORRS

,

ORNS

,

EORS

,

BICS

,

TEQ

or

TST

, the carry flag is updated to bit[0] of the register

Rm.

34.2.3.5 Address alignment

An aligned access is an operation where a word-aligned address is used for a word, dual

word, or multiple word access, or where a halfword-aligned address is used for a halfword

access. Byte accesses are always aligned.

The Cortex-M3 processor supports unaligned access only for the following instructions:

•

LDR

,

LDRT

•

LDRH

,

LDRHT

•

LDRSH

,

LDRSHT

•

STR

,

STRT

•

STRH

,

STRHT

All other load and store instructions generate a usage fault exception if they perform an

unaligned access, and therefore their accesses must be address aligned. For more

information about usage faults see Section 34.3.4 “

Fault handling”.

Unaligned accesses are usually slower than aligned accesses. In addition, some memory

regions might not support unaligned accesses. Therefore, ARM recommends that

programmers ensure that accesses are aligned. To avoid accidental generation of

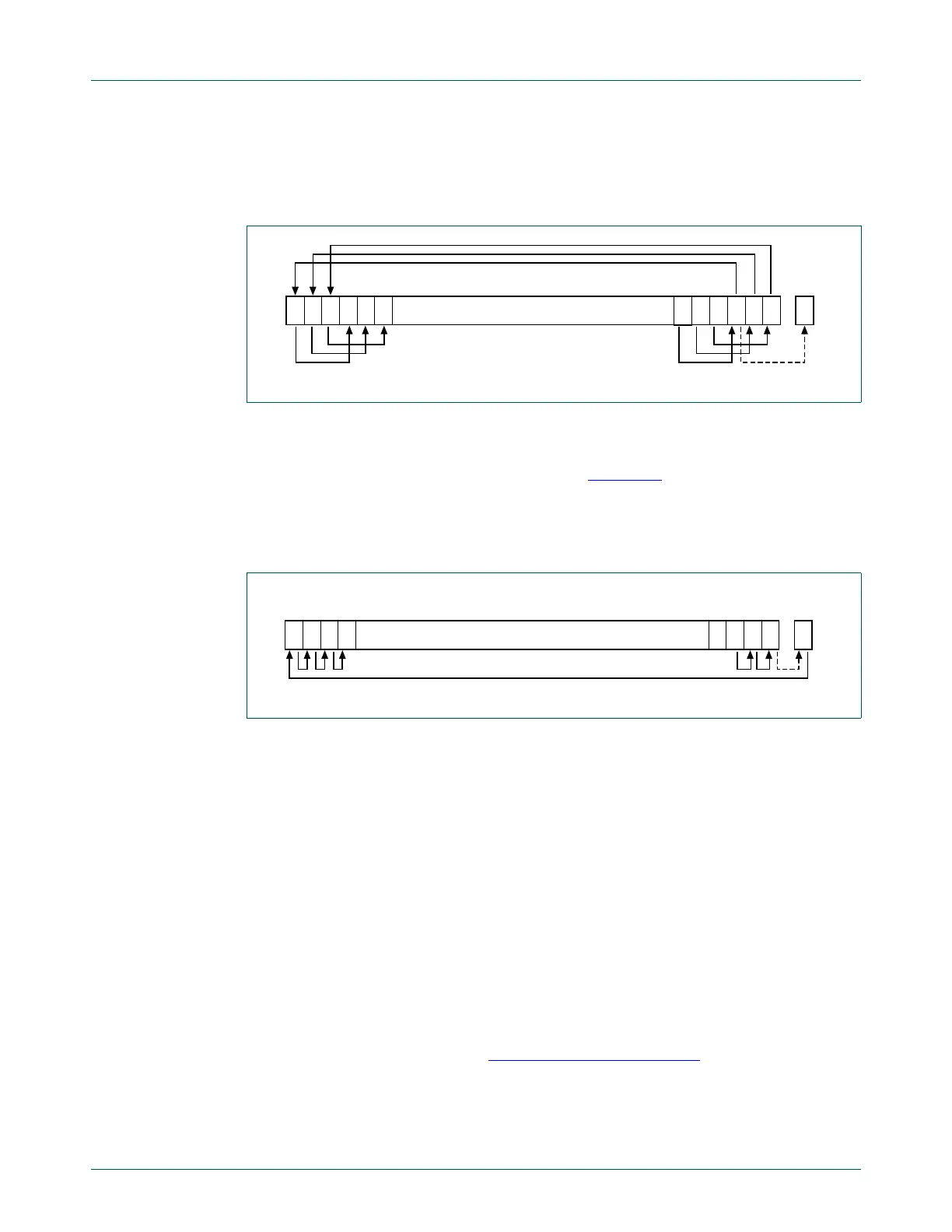

Fig 144. ROR#3

Fig 145. RRX

Loading...

Loading...