UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 164 of 841

NXP Semiconductors

UM10360

Chapter 10: LPC176x/5x Ethernet

distributed over two registers TSV0 and TSV1. These registers are provided for debug

purposes, because the communication between driver software and the Ethernet block

takes place primarily through the frame descriptors. The status register contents are valid

as long as the internal status of the MAC is valid and should typically only be read when

the transmit and receive processes are halted.

Table 160

lists the bit definitions of the TSV0 register.

[1] The EMAC doesn't distinguish the frame type and frame length, so, e.g. when the IP(0x8000) or

ARP(0x0806) packets are received, it compares the frame type with the max length and gives the "Length

out of range" error. In fact, this bit is not an error indication, but simply a statement by the chip regarding the

status of the received frame.

10.12.14 Transmit Status Vector 1 Register (TSV1 - 0x5000 015C)

The Transmit Status Vector 1 register (TSV1) is a read-only register with an address of

0x5000 015C. The transmit status vector registers store the most recent transmit status

returned by the MAC. Since the status vector consists of more than 4 bytes, status is

distributed over two registers TSV0 and TSV1. These registers are provided for debug

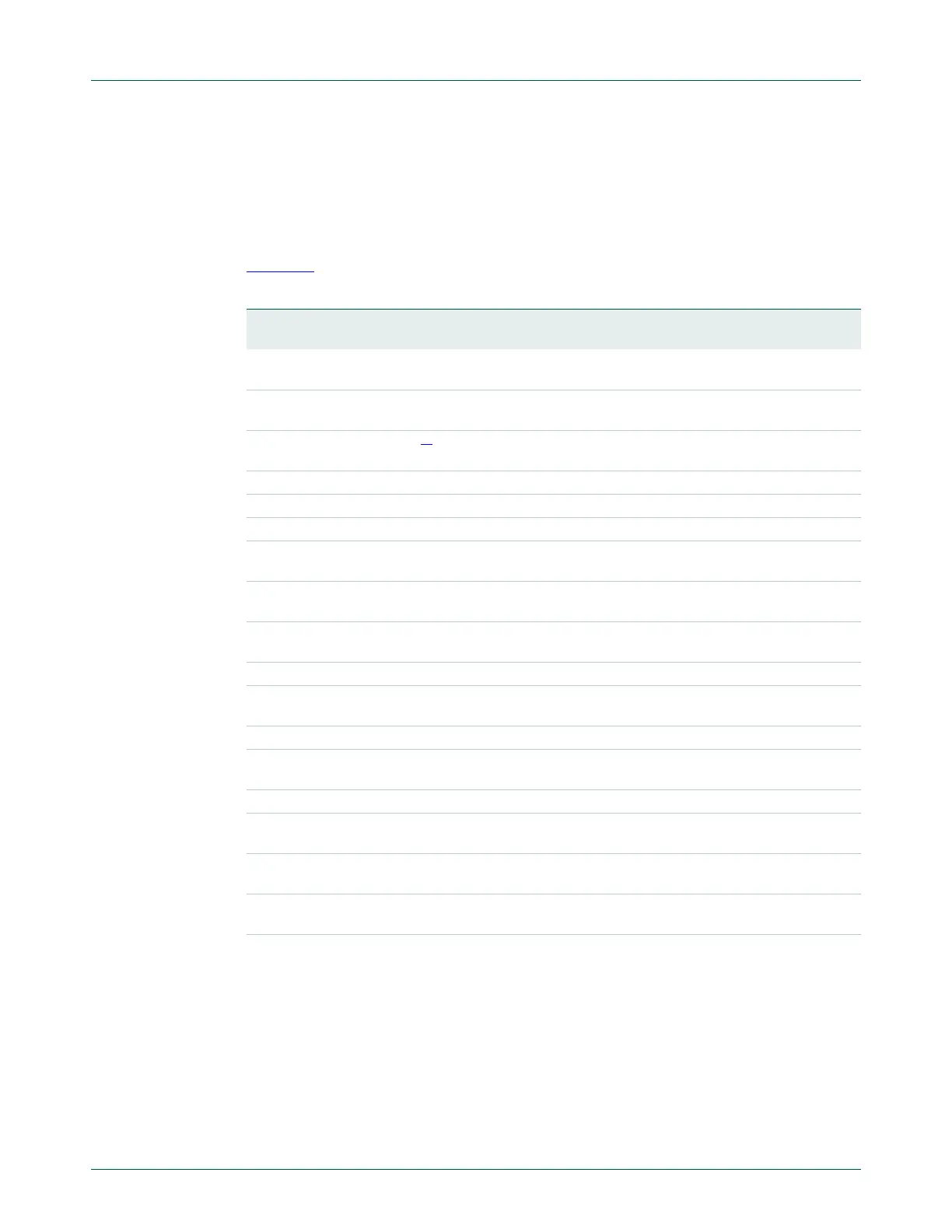

Table 160. Transmit Status Vector 0 register (TSV0 - address 0x5000 0158) bit description

Bit Symbol Function Reset

value

0 CRC error The attached CRC in the packet did not match the

internally generated CRC.

0

1 Length check error Indicates the frame length field does not match the actual

number of data items and is not a type field.

0

2 Length out of range

[1]

Indicates that frame type/length field was larger than

1500 bytes.

0

3 Done Transmission of packet was completed. 0

4 Multicast Packet’s destination was a multicast address. 0

5 Broadcast Packet’s destination was a broadcast address. 0

6 Packet Defer Packet was deferred for at least one attempt, but less than

an excessive defer.

0

7 Excessive Defer Packet was deferred in excess of 6071 nibble times in

100 Mbps or 24287 bit times in 10 Mbps mode.

0

8 Excessive Collision Packet was aborted due to exceeding of maximum allowed

number of collisions.

0

9 Late Collision Collision occurred beyond collision window, 512 bit times. 0

10 Giant Byte count in frame was greater than can be represented

in the transmit byte count field in TSV1.

0

11 Underrun Host side caused buffer underrun. 0

27:12 Total bytes The total number of bytes transferred including collided

attempts.

0x0

28 Control frame The frame was a control frame. 0

29 Pause The frame was a control frame with a valid PAUSE

opcode.

0

30 Backpressure Carrier-sense method backpressure was previously

applied.

0

31 VLAN Frame’s length/type field contained 0x8100 which is the

VLAN protocol identifier.

0

Loading...

Loading...