UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 231 of 841

NXP Semiconductors

UM10360

Chapter 11: LPC176x/5x USB device controller

USBEpIntPri is a write-only register.

11.10.4 Endpoint realization registers

The registers in this group allow realization and configuration of endpoints at run time.

11.10.4.1 EP RAM requirements

The USB device controller uses a RAM based FIFO for each endpoint buffer. The RAM

dedicated for this purpose is called the Endpoint RAM (EP_RAM). Each endpoint has

space reserved in the EP_RAM. The EP_RAM space required for an endpoint depends

on its MaxPacketSize and whether it is double buffered. 32 words of EP_RAM are used by

the device for storing the endpoint buffer pointers. The EP_RAM is word aligned but the

MaxPacketSize is defined in bytes hence the RAM depth has to be adjusted to the next

word boundary. Also, each buffer has one word header showing the size of the packet

length received.

The EP_ RAM space (in words) required for the physical endpoint can be expressed as

(1)

where dbstatus = 1 for a single-buffered endpoint and 2 for a double-buffered endpoint.

Since all the realized endpoints occupy EP_RAM space, the total EP_RAM requirement is

(2)

where N is the number of realized endpoints. Total EP_RAM space should not exceed

4096 bytes (4 kB, 1 kwords).

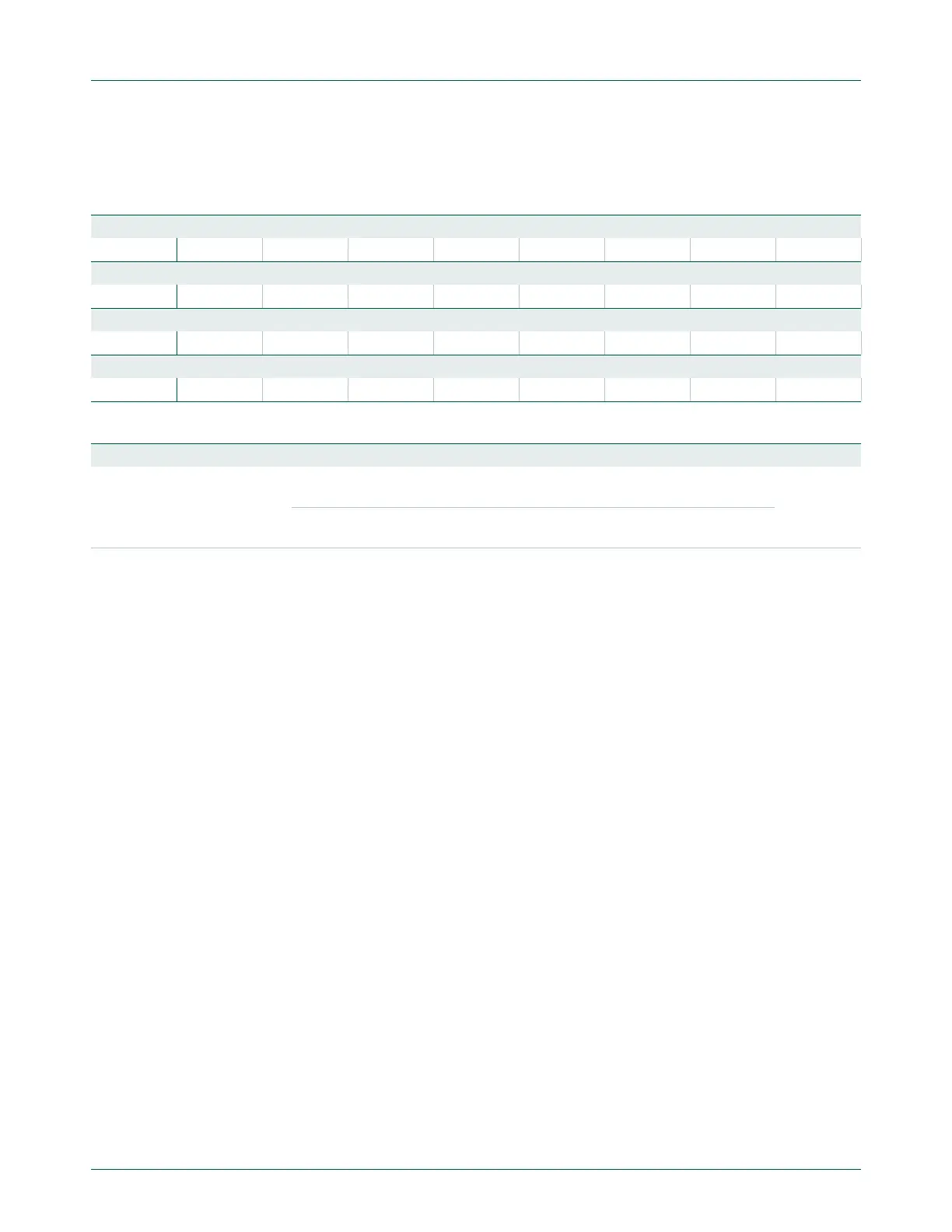

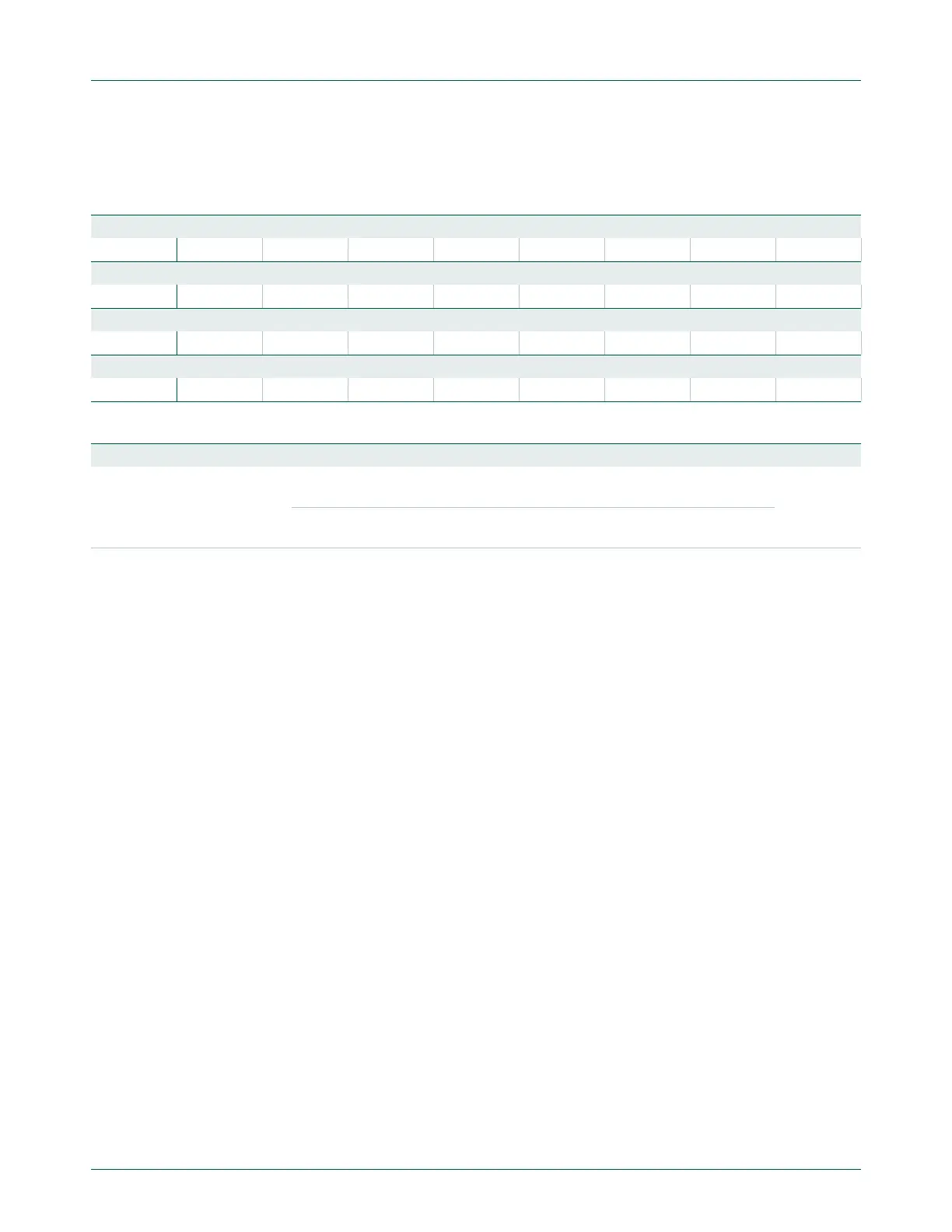

Table 209. USB Endpoint Interrupt Priority register (USBEpIntPri - address 0x5000 C240) bit allocation

Reset value: 0x0000 0000

Bit 31 30 29 28 27 26 25 24

Symbol

EP15TX EP15RX EP14TX E14RX EP13TX EP13RX EP12TX EP12RX

Bit 23 22 21 20 19 18 17 16

Symbol

EP11TX EP11RX EP10TX EP10RX EP9TX EP9RX EP8TX EP8RX

Bit 15 14 13 12 11 10 9 8

Symbol

EP7TX EP7RX EP6TX EP6RX EP5TX EP5RX EP4TX EP4RX

Bit 7 6 5 4 3 2 1 0

Symbol

EP3TX EP3RX EP2TX EP2RX EP1TX EP1RX EP0TX EP0RX

Table 210. USB Endpoint Interrupt Priority register (USBEpIntPri - address 0x5000 C240) bit description

Bit Symbol Value Description Reset value

31:0 See USBEpIntPri bit

allocation table above

0 The corresponding interrupt is routed to the EP_SLOW bit of

USBDevIntSt

0

1 The corresponding interrupt is routed to the EP_FAST bit of

USBDevIntSt

EPRAMspace

MaxPacketSize 3+

4

--------------------------------------------------

1+

dbstatus=

TotalEPRAMspace 32 EPRAMspace n

n0=

N

+=

Loading...

Loading...