UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 370 of 841

NXP Semiconductors

UM10360

Chapter 16: LPC176x/5x CAN1/2

16.7.16 CAN Transmit Data register B (CAN1TDB[1/2/3] -

0x4004 40[3C/4C/5C], CAN2TDB[1/2/3] - 0x4004 80[3C/4C/5C])

When the corresponding TBS bit in CANSR is 1, software can write to one of these

registers to define the 5th through 8th data bytes of the next transmit message. The Data

Length Code defines the number of transferred data bytes. The first bit transmitted is the

most significant bit of TX Data Byte 1.

16.7.17 CAN Sleep Clear register (CANSLEEPCLR - 0x400F C110)

This register provides the current sleep state of the two CAN channels and provides a

means to restore the clocks to that channel following wake-up. Refer to Section 16.8.2

“Sleep mode” for more information on the CAN sleep feature.

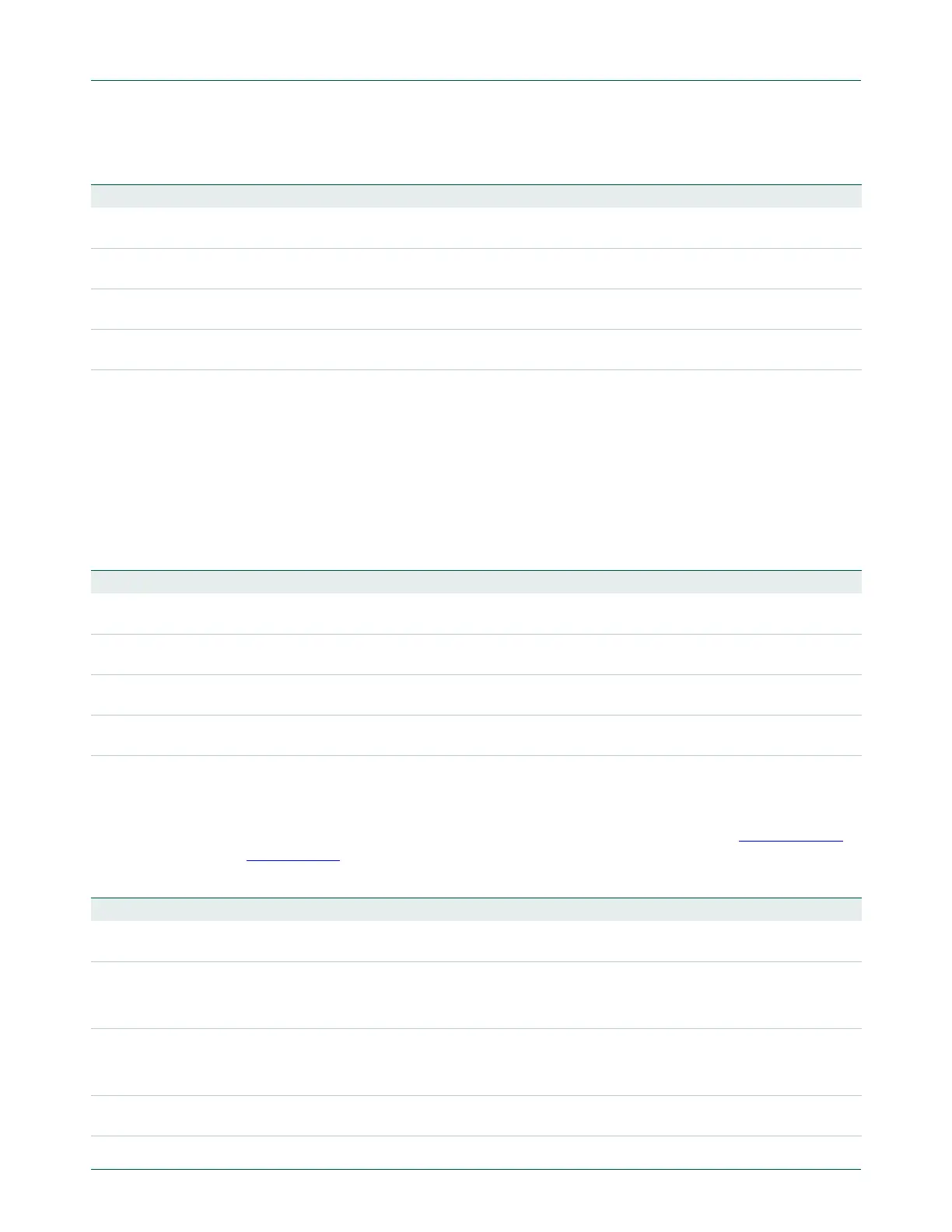

Table 333. CAN Transmit Data register A (CAN1TDA[1/2/3] - address 0x4004 40[38/48/58], CAN2TDA[1/2/3] - address

0x4004 80[38/48/58]) bit description

Bit Symbol Function Reset Value RM Set

7:0 Data 1 If RTR = 0 and DLC ³ 0001 in the corresponding CANxTFI, this byte is sent as the

first Data byte of the next transmit message.

0X

15;8 Data 2 If RTR = 0 and DLC ³ 0010 in the corresponding CANxTFI, this byte is sent as the

2nd Data byte of the next transmit message.

0X

23:16 Data 3 If RTR = 0 and DLC ³ 0011 in the corresponding CANxTFI, this byte is sent as the

3rd Data byte of the next transmit message.

0X

31:24 Data 4 If RTR = 0 and DLC ³ 0100 in the corresponding CANxTFI, this byte is sent as the

4th Data byte of the next transmit message.

0X

Table 334. CAN Transmit Data register B (CAN1TDB[1/2/3] - address 0x4004 40[3C/4C/5C], CAN2TDB[1/2/3] - address

0x4004 80[3C/4C/5C]) bit description

Bit Symbol Function Reset Value RM Set

7:0 Data 5 If RTR = 0 and DLC ³ 0101 in the corresponding CANTFI, this byte is sent as the

5th Data byte of the next transmit message.

0X

15;8 Data 6 If RTR = 0 and DLC ³ 0110 in the corresponding CANTFI, this byte is sent as the

6th Data byte of the next transmit message.

0X

23:16 Data 7 If RTR = 0 and DLC ³ 0111 in the corresponding CANTFI, this byte is sent as the

7th Data byte of the next transmit message.

0X

31:24 Data 8 If RTR = 0 and DLC ³ 1000 in the corresponding CANTFI, this byte is sent as the

8th Data byte of the next transmit message.

0X

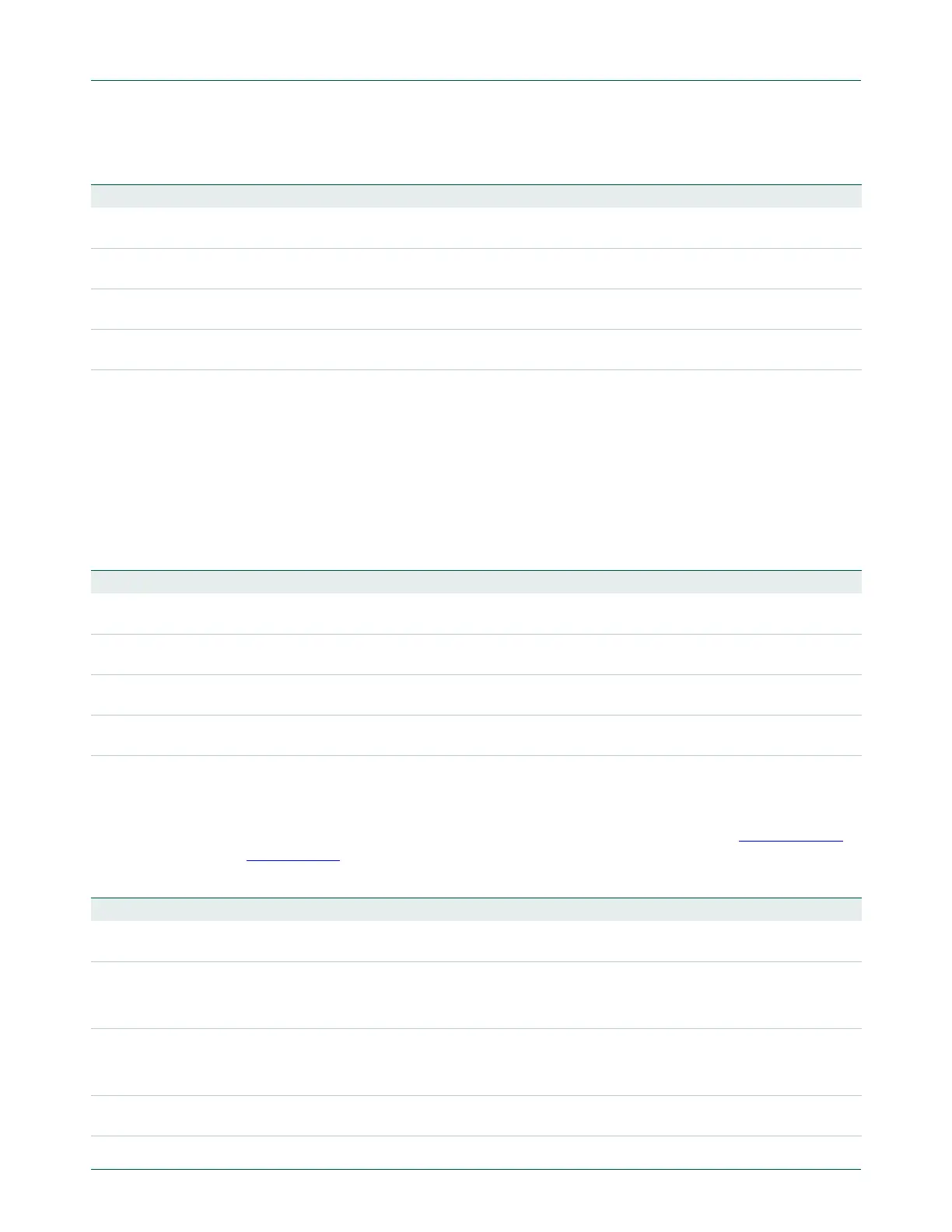

Table 335. CAN Sleep Clear register (CANSLEEPCLR - address 0x400F C110) bit description

Bit Symbol Function Reset Value

0 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

1 CAN1SLEEP Sleep status and control for CAN channel 1.

Read: when 1, indicates that CAN channel 1 is in the sleep mode.

Write: writing a 1 causes clocks to be restored to CAN channel 1.

0

2 CAN2SLEEP Sleep status and control for CAN channel 2.

Read: when 1, indicates that CAN channel 2 is in the sleep mode.

Write: writing a 1 causes clocks to be restored to CAN channel 2.

0

31:3 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

Loading...

Loading...