UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 77 of 841

NXP Semiconductors

UM10360

Chapter 6: LPC176x/5x Nested Vectored Interrupt Controller (NVIC)

6.5 Register description

The following table summarizes the registers in the NVIC as implemented in the

LPC176x/5x. The Cortex-M3 User Guide Section 34.4.2

provides a functional description

of the NVIC.

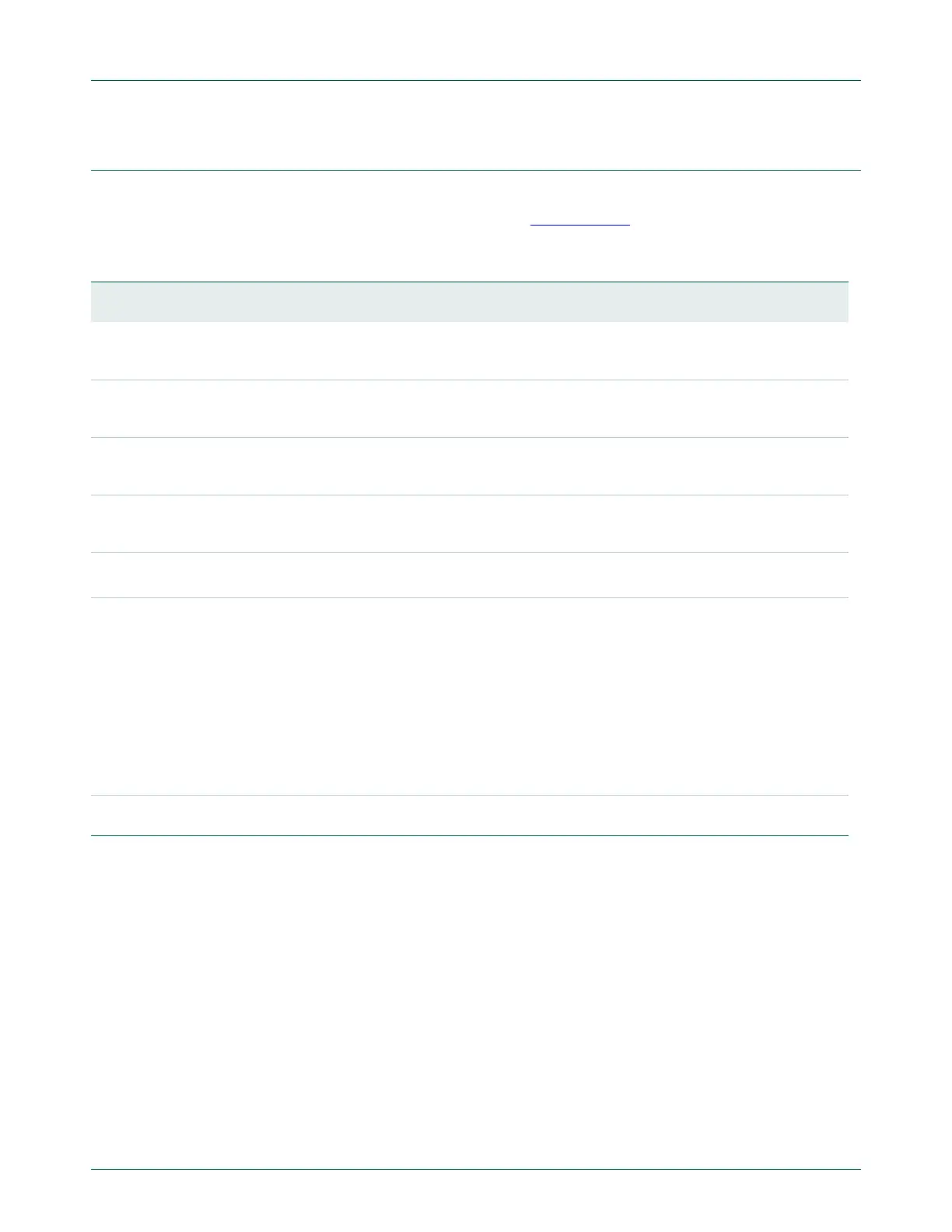

Table 51. NVIC register map

Name Description Access Reset

value

Address

ISER0 to

ISER1

Interrupt Set-Enable Registers. These 2 registers allow enabling

interrupts and reading back the interrupt enables for specific

peripheral functions.

RW 0 ISER0 - 0xE000 E100

ISER1 - 0xE000 E104

ICER0 to

ICER1

Interrupt Clear-Enable Registers. These 2 registers allow disabling

interrupts and reading back the interrupt enables for specific

peripheral functions.

RW 0 ICER0 - 0xE000 E180

ICER1 - 0xE000 E184

ISPR0 to

ISPR1

Interrupt Set-Pending Registers. These 2 registers allow changing

the interrupt state to pending and reading back the interrupt

pending state for specific peripheral functions.

RW 0 ISPR0 - 0xE000 E200

ISPR1 - 0xE000 E204

ICPR0 to

ICPR1

Interrupt Clear-Pending Registers. These 2 registers allow

changing the interrupt state to not pending and reading back the

interrupt pending state for specific peripheral functions.

RW 0 ICPR0 - 0xE000 E280

ICPR1 - 0xE000 E284

IABR0 to

IABR1

Interrupt Active Bit Registers. These 2 registers allow reading the

current interrupt active state for specific peripheral functions.

RO 0 IABR0 - 0xE000 E300

IABR1 - 0xE000 E304

IPR0 to

IPR8

Interrupt Priority Registers. These 9 registers allow assigning a

priority to each interrupt. Each register contains the 5-bit priority

fields for 4 interrupts.

RW 0 IPR0 - 0xE000 E400

IPR1 - 0xE000 E404

IPR2 - 0xE000 E408

IPR3 - 0xE000 E40C

IPR4 - 0xE000 E410

IPR5 - 0xE000 E414

IPR6 - 0xE000 E418

IPR7 - 0xE000 E41C

IPR8 - 0xE000 E420

STIR Software Trigger Interrupt Register. This register allows software to

generate an interrupt.

WO 0 STIR - 0xE000 EF00

Loading...

Loading...