UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 233 of 841

NXP Semiconductors

UM10360

Chapter 11: LPC176x/5x USB device controller

}

/* Clear the EP_RLZED bit */

Clear EP_RLZED bit in USBDevIntSt;

}

The device will not respond to any transactions to unrealized endpoints. The SIE

Configure Device command will only cause realized and enabled endpoints to respond to

transactions. For details see Table 243

.

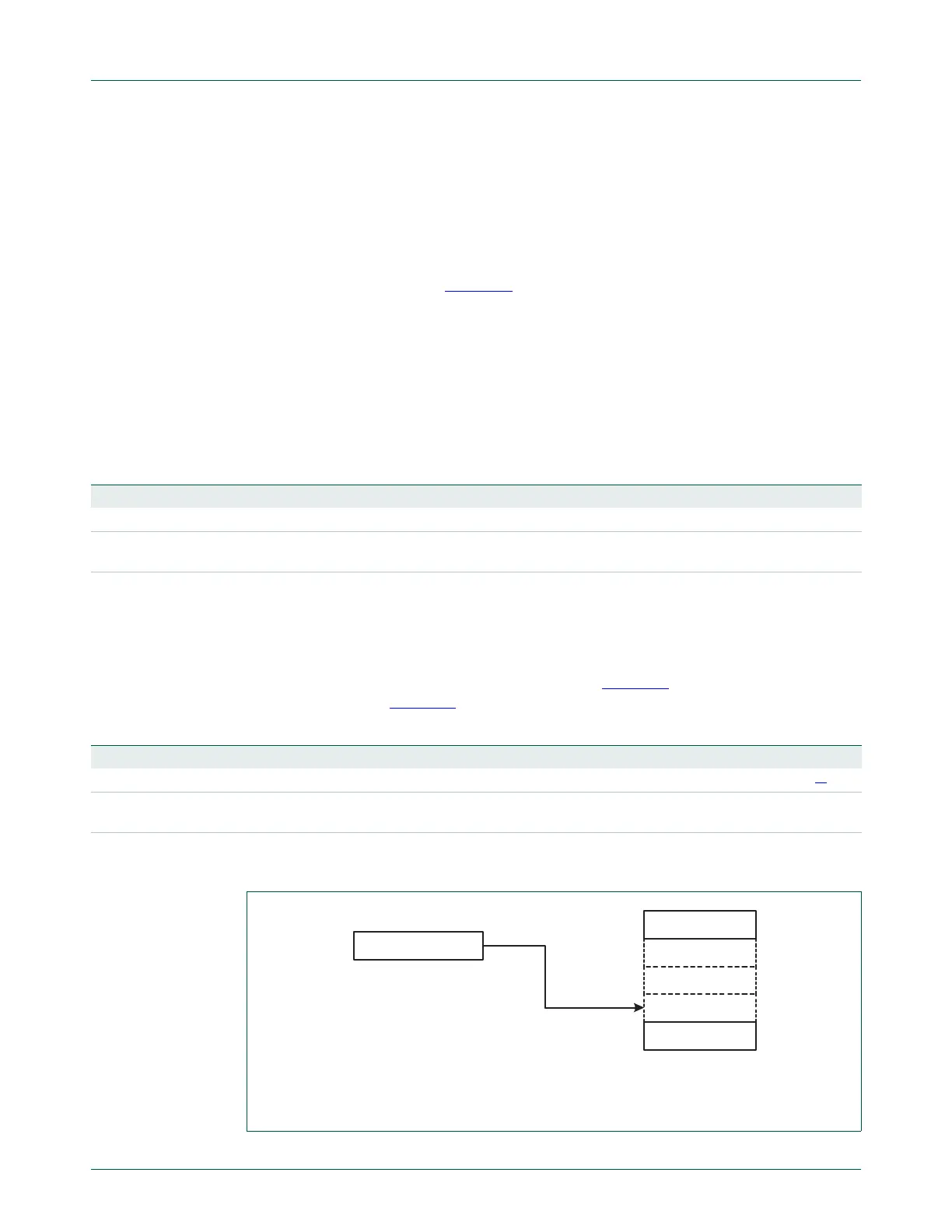

11.10.4.3 USB Endpoint Index register (USBEpIn - 0x5000 C248)

Each endpoint has a register carrying the MaxPacketSize value for that endpoint. This is

in fact a register array. Hence before writing, this register is addressed through the

USBEpIn register.

The USBEpIn register will hold the physical endpoint number. Writing to USBMaxPSize

will set the array element pointed to by USBEpIn. USBEpIn is a write-only register.

11.10.4.4 USB MaxPacketSize register (USBMaxPSize - 0x5000 C24C)

On reset, the control endpoint is assigned the maximum packet size of 8 bytes. Other

endpoints are assigned 0. Modifying USBMaxPSize will cause the endpoint buffer

addresses within the EP_RAM to be recalculated. This is a multi-cycle process. At the

end, the EP_RLZED bit will be set in USBDevIntSt (Table 192

). USBMaxPSize array

indexing is shown in Figure 28

. USBMaxPSize is a read/write register.

[1] Reset value for EP0 and EP1. All other endpoints have a reset value of 0x0.

Table 213. USB Endpoint Index register (USBEpIn - address 0x5000 C248) bit description

Bit Symbol Description Reset value

4:0 PHY_EP Physical endpoint number (0-31) 0

31:5 - Reserved, user software should not write ones to reserved bits. The value read from

a reserved bit is not defined.

NA

Table 214. USB MaxPacketSize register (USBMaxPSize - address 0x5000 C24C) bit description

Bit Symbol Description Reset value

9:0 MPS The maximum packet size value. 0x008

[1]

31:10 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

The Endpoint Index is set via the USBEpIn register. MPS_EP0 to MPS_EP31 are accessed via the

USBMaxPSize register.

Fig 28. USB MaxPacketSize register array indexing

ENDPOINT INDEX

MPS_EP0

MPS_EP31

Loading...

Loading...