UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 536 of 841

NXP Semiconductors

UM10360

Chapter 25: LPC176x/5x Motor control PWM

25.7.8 MCPWM Dead-time register (MCDT - 0x400B 803C)

This register holds the dead-time values for the three channels. If a channel’s DTE bit in

MCCON is 1 to enable its dead-time counter, the counter counts down from this value

whenever one its channel’s outputs changes from “active” to “passive” state. When the

dead-time counter reaches 0, the channel changes its other output from “passive” to

“active” state.

The motivation for the dead-time feature is that power transistors, like those driven by the

A and B outputs in a motor-control application, take longer to fully turn off than they take to

start to turn on. If the A and B transistors are ever turned on at the same time, a wasteful

and damaging current will flow between the power rails through the transistors. In such

applications, the dead-time register should be programmed with the number of PCLK

periods that is greater than or equal to the transistors’ maximum turn-off time minus their

minimum turn-on time.

[1] If ACMODE is 1 selecting AC-mode, this field controls the dead time for all three channels.

[2] If ACMODE is 0.

25.7.9 MCPWM Commutation Pattern register (MCCP - 0x400B 8040)

This register is used in DC mode only. The internal MCOA0 signal is routed to any or all of

the six output pins under the control of the bits in this register. Like the Match and Limit

registers, this register has “write” and “operational” versions. See 25.7.6

and 25.8.2 for

more about this subject.

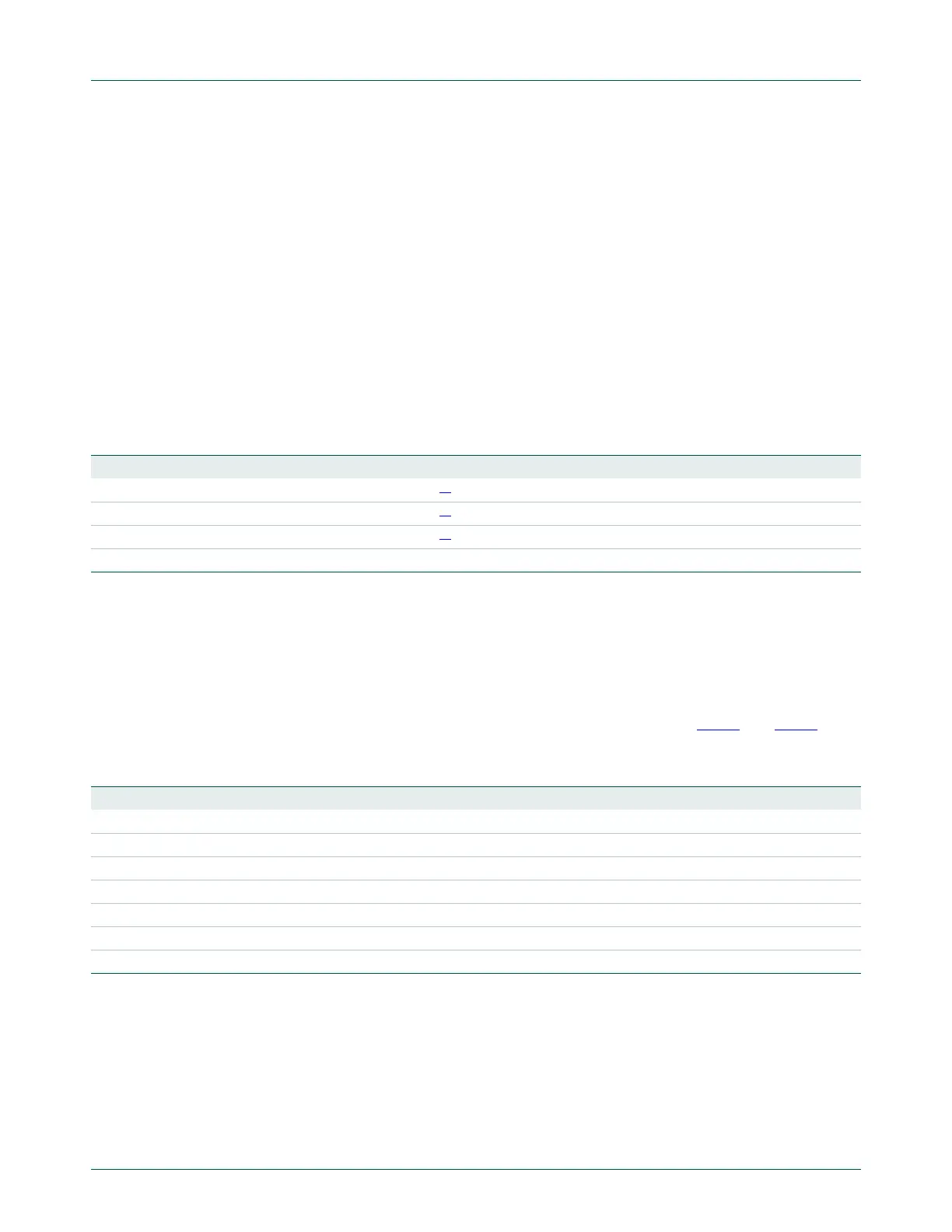

Table 475. MCPWM Dead-time register (MCDT - address 0x400B 803C) bit description

Bit Symbol Description Reset value

9:0 DT0 Dead time for channel 0.

[1]

0x3FF

19:10 DT1 Dead time for channel 1.

[2]

0x3FF

29:20 DT2 Dead time for channel 2.

[2]

0x3FF

31:30 - reserved

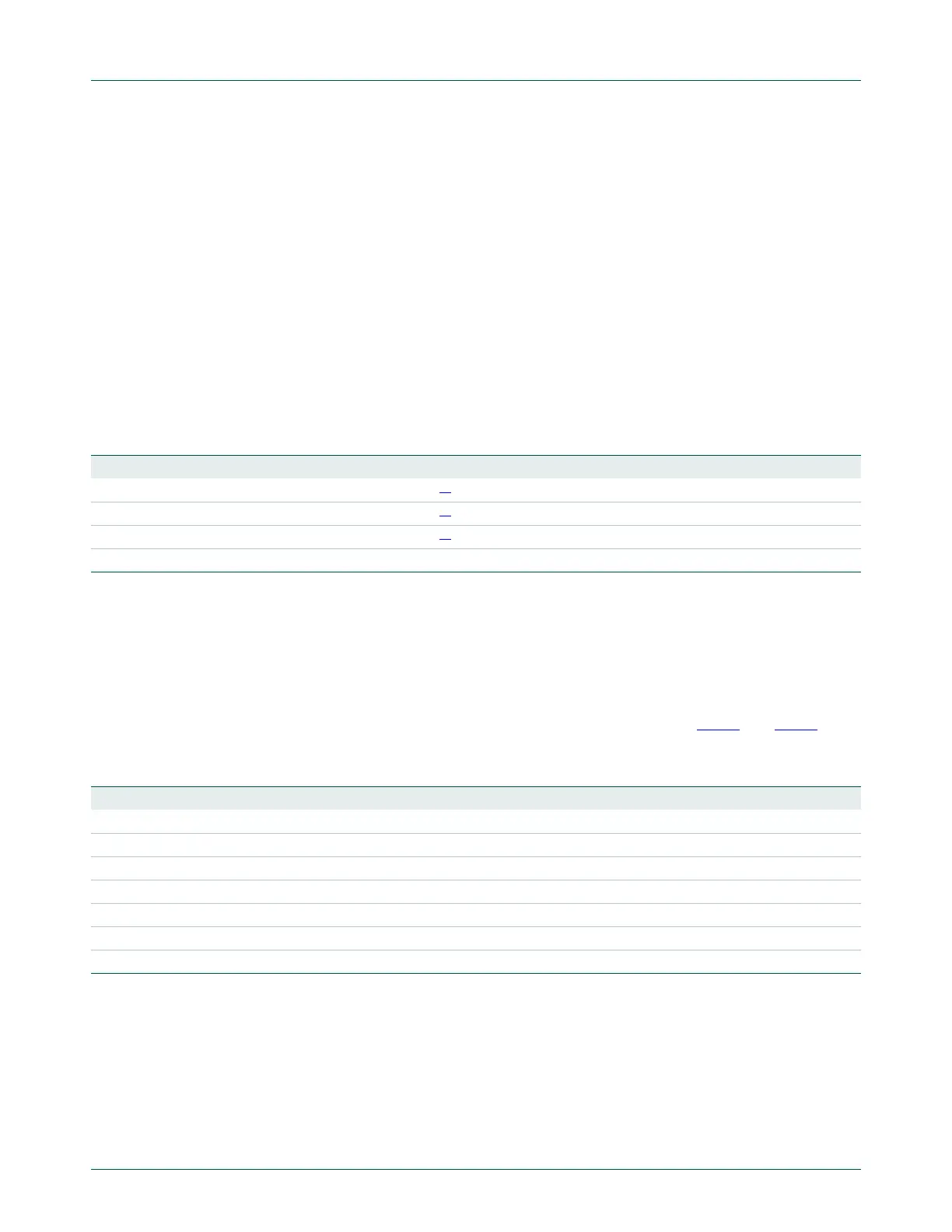

Table 476. MCPWM Commutation Pattern register (MCCP - address 0x400B 8040) bit description

Bit Symbol Description Reset value

0 CCPA0 0 = MCOA0 passive, 1 = internal MCOA0. 0

1 CCPB0 0 = MCOB0 passive, 1 = MCOB0 tracks internal MCOA0. 0

2 CCPA1 0 = MCOA1 passive, 1 = MCOA1 tracks internal MCOA0. 0

3 CCPB1 0 = MCOB1 passive, 1 = MCOB1 tracks internal MCOA0. 0

4 CCPA2 0 = MCOA2 passive, 1 = MCOA2 tracks internal MCOA0. 0

5 CCPB2 0 = MCOB2 passive, 1 = MCOB2 tracks internal MCOA0. 0

31:6 - Reserved.

Loading...

Loading...