UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 352 of 841

NXP Semiconductors

UM10360

Chapter 16: LPC176x/5x CAN1/2

The internal registers of each CAN Controller appear to the CPU as on-chip memory

mapped peripheral registers. Because the CAN Controller can operate in different modes

(Operating/Reset, see also Section 16.7.1 “

CAN Mode register (CAN1MOD -

0x4004 4000, CAN2MOD - 0x4004 8000)”), one has to distinguish between different

internal address definitions. Note that write access to some registers is only allowed in

Reset Mode.

In the following register tables, the column “Reset Value” shows how a hardware reset

affects each bit or field, while the column “RM Set” indicates how each bit or field is

affected if software sets the RM bit, or RM is set because of a Bus-Off condition. Note that

while hardware reset sets RM, in this case the setting noted in the “Reset Value” column

prevails over that shown in the “RM Set” column, in the few bits where they differ. In both

columns, X indicates the bit or field is unchanged.

16.7.1 CAN Mode register (CAN1MOD - 0x4004 4000, CAN2MOD -

0x4004 8000)

The contents of the Mode Register are used to change the behavior of the CAN

Controller. Bits may be set or reset by the CPU that uses the Mode Register as a

read/write memory.

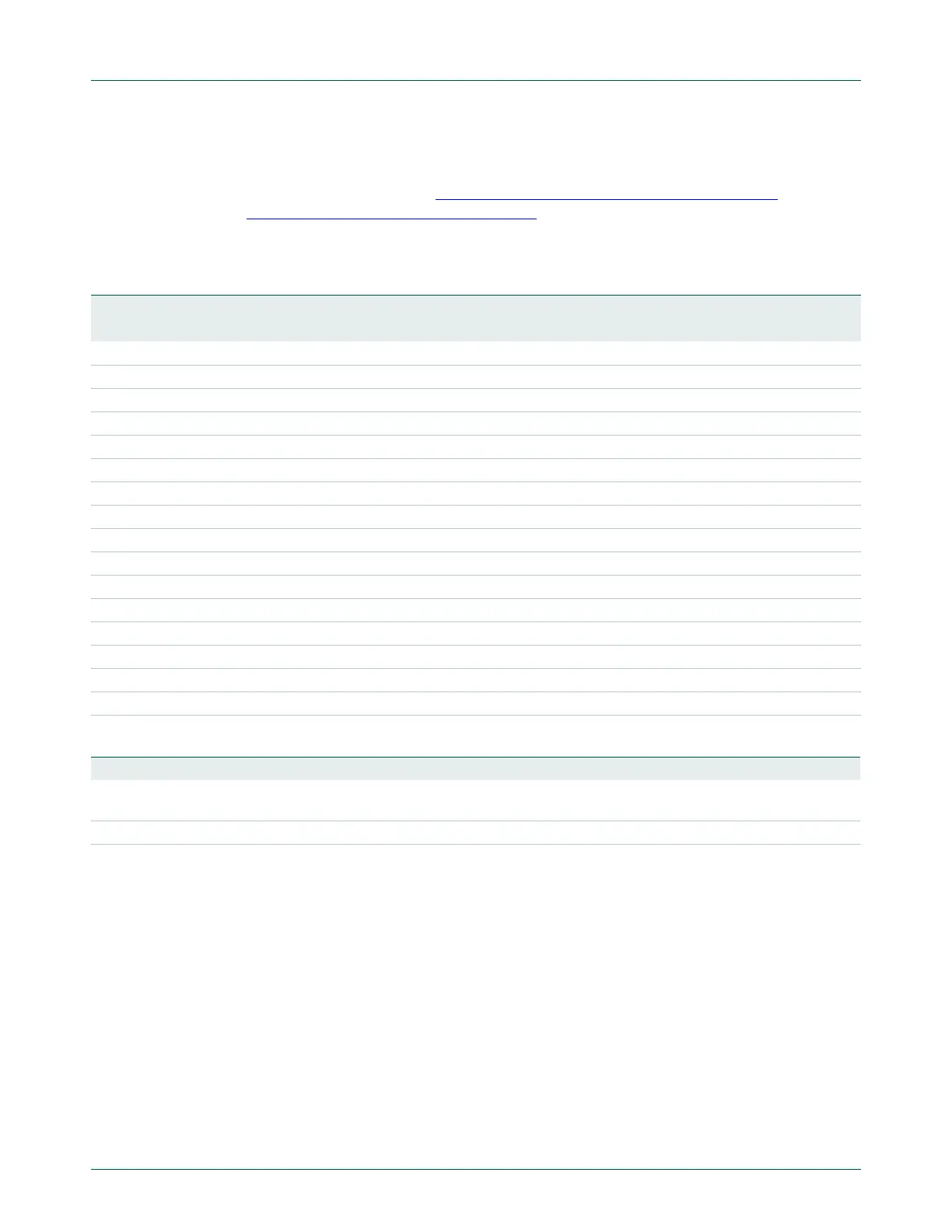

Table 315. CAN1 and CAN2 controller register summary

Generic

Name

Operating Mode Reset Mode

Read Write Read Write

MOD Mode Mode Mode Mode

CMR 0x00 Command 0x00 Command

GSR Global Status and Error Counters - Global Status and Error Counters Error Counters only

ICR Interrupt and Capture - Interrupt and Capture -

IER Interrupt Enable Interrupt Enable Interrupt Enable Interrupt Enable

BTR Bus Timing - Bus Timing Bus Timing

EWL Error Warning Limit - Error Warning Limit Error Warning Limit

SR Status - Status -

RFS Rx Info and Index - Rx Info and Index Rx Info and Index

RID Rx Identifier - Rx Identifier Rx Identifier

RDA Rx Data - Rx Data Rx Data

RDB Rx Info and Index - Rx Info and Index Rx Info and Index

TFI1 Tx Info1 Tx Info Tx Info Tx Info

TID1 Tx Identifier Tx Identifier Tx Identifier Tx Identifier

TDA1 Tx Data Tx Data Tx Data Tx Data

TDB1 Tx Data Tx Data Tx Data Tx Data

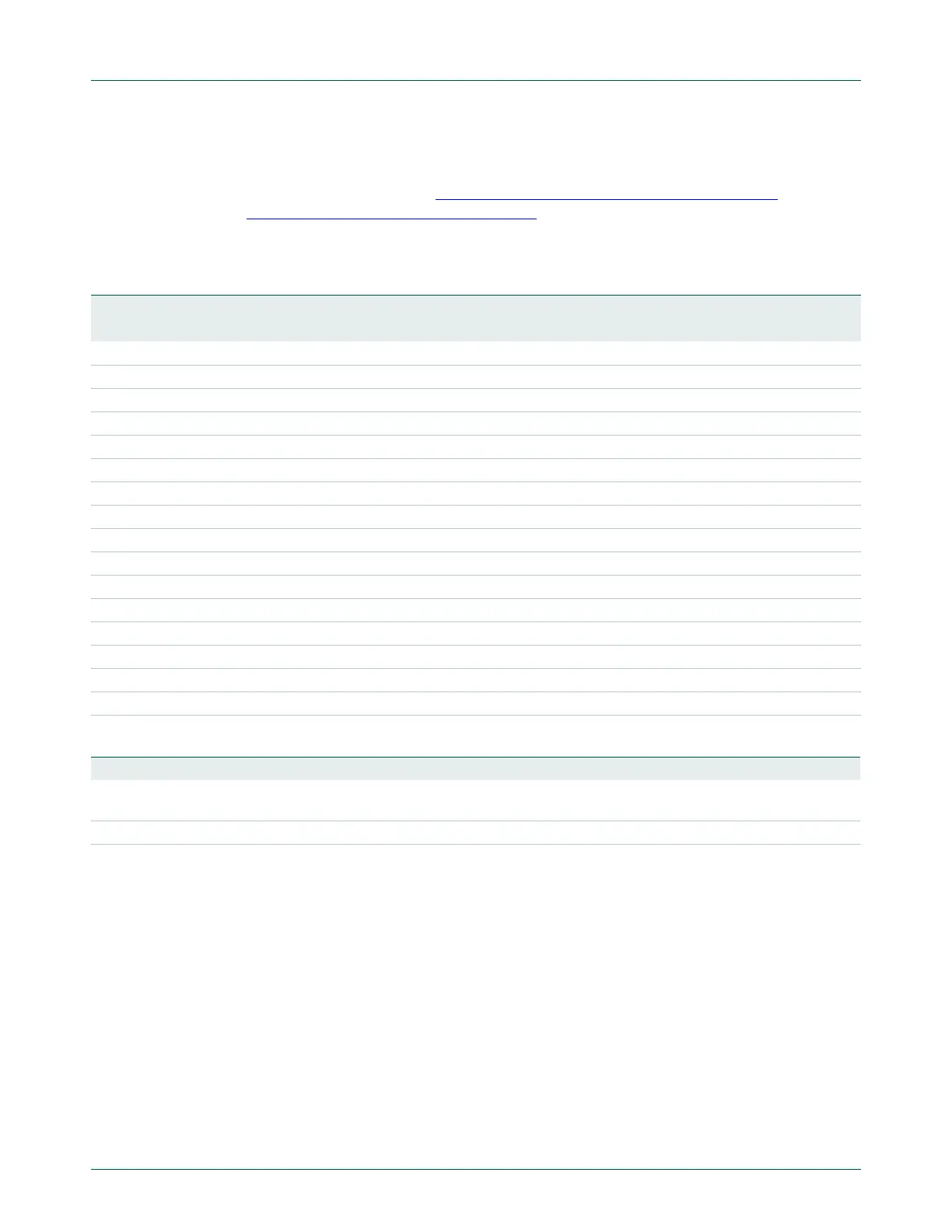

Table 316. CAN Wake and Sleep registers

Name Description Access Reset Value Address

CANSLEEPCLR Allows clearing the current CAN channel sleep state as well as

reading that state.

R/W 0 0x400F C110

CANWAKEFLAGS Allows reading the wake-up state of the CAN channels. R/W 0 0x400F C114

Loading...

Loading...