UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 149 of 841

NXP Semiconductors

UM10360

Chapter 10: LPC176x/5x Ethernet

10.10 Registers and software interface

The software interface of the Ethernet block consists of a register view and the format

definitions for the transmit and receive descriptors. These two aspects are addressed in

the next two subsections.

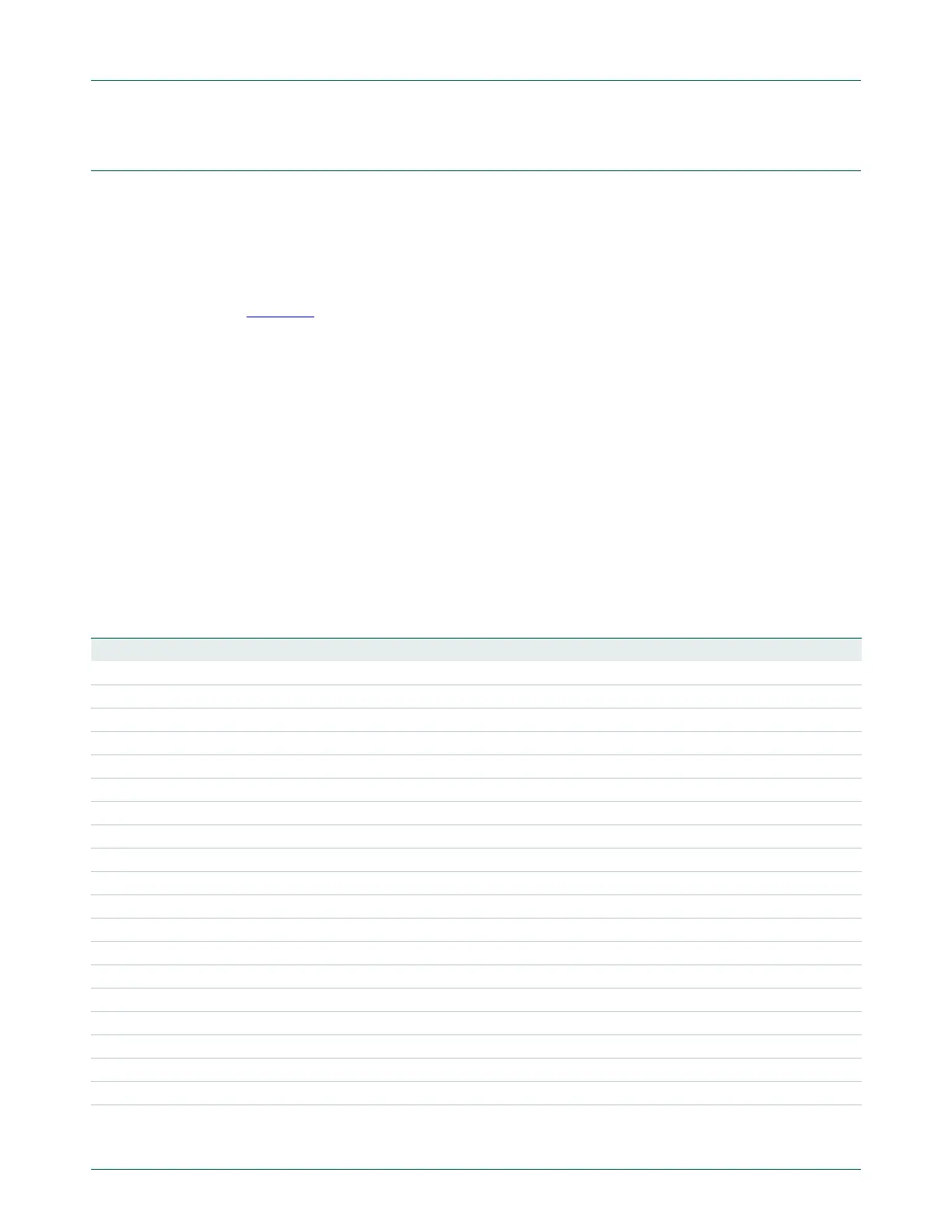

10.10.1 Register map

Table 128 lists the registers, register addresses and other basic information. The total

AHB address space required is 4 kilobytes.

After a hard reset or a soft reset via the RegReset bit of the Command register all bits in

all registers are reset to 0 unless stated otherwise in the following register descriptions.

Some registers will have unused bits which will return a 0 on a read via the AHB interface.

Writing to unused register bits of an otherwise writable register will not have side effects.

The register map consists of registers in the Ethernet MAC and registers around the core

for controlling DMA transfers, flow control and filtering.

Reading from reserved addresses or reserved bits leads to unpredictable data. Writing to

reserved addresses or reserved bits has no effect.

Reading of write-only registers will return a read error on the AHB interface. Writing of

read-only registers will return a write error on the AHB interface.

Table 128. Ethernet register definitions

Name Description Access Reset Value Address

MAC registers

MAC1 MAC configuration register 1. R/W 0x8000 0x5000 0000

MAC2 MAC configuration register 2. R/W 0 0x5000 0004

IPGT Back-to-Back Inter-Packet-Gap register. R/W 0 0x5000 0008

IPGR Non Back-to-Back Inter-Packet-Gap register. R/W 0 0x5000 000C

CLRT Collision window / Retry register. R/W 0x370F 0x5000 0010

MAXF Maximum Frame register. R/W 0x0600 0x5000 0014

SUPP PHY Support register. R/W 0 0x5000 0018

TEST Test register. R/W 0 0x5000 001C

MCFG MII Mgmt Configuration register. R/W 0 0x5000 0020

MCMD MII Mgmt Command register. R/W 0 0x5000 0024

MADR MII Mgmt Address register. R/W 0 0x5000 0028

MWTD MII Mgmt Write Data register. WO 0 0x5000 002C

MRDD MII Mgmt Read Data register. RO 0 0x5000 0030

MIND MII Mgmt Indicators register. RO 0 0x5000 0034

SA0 Station Address 0 register. R/W 0 0x5000 0040

SA1 Station Address 1 register. R/W 0 0x5000 0044

SA2 Station Address 2 register. R/W 0 0x5000 0048

Control registers

Command Command register. R/W 0 0x5000 0100

Loading...

Loading...