UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 20 December 2013 793 of 841

NXP Semiconductors

UM10360

Chapter 34: Appendix: Cortex-M3 user guide

34.4.5.6 MPU access permission attributes

This section describes the MPU access permission attributes. The access permission

bits, TEX, C, B, S, AP, and XN, of the RASR, control access to the corresponding memory

region. If an access is made to an area of memory without the required permissions, then

the MPU generates a permission fault.

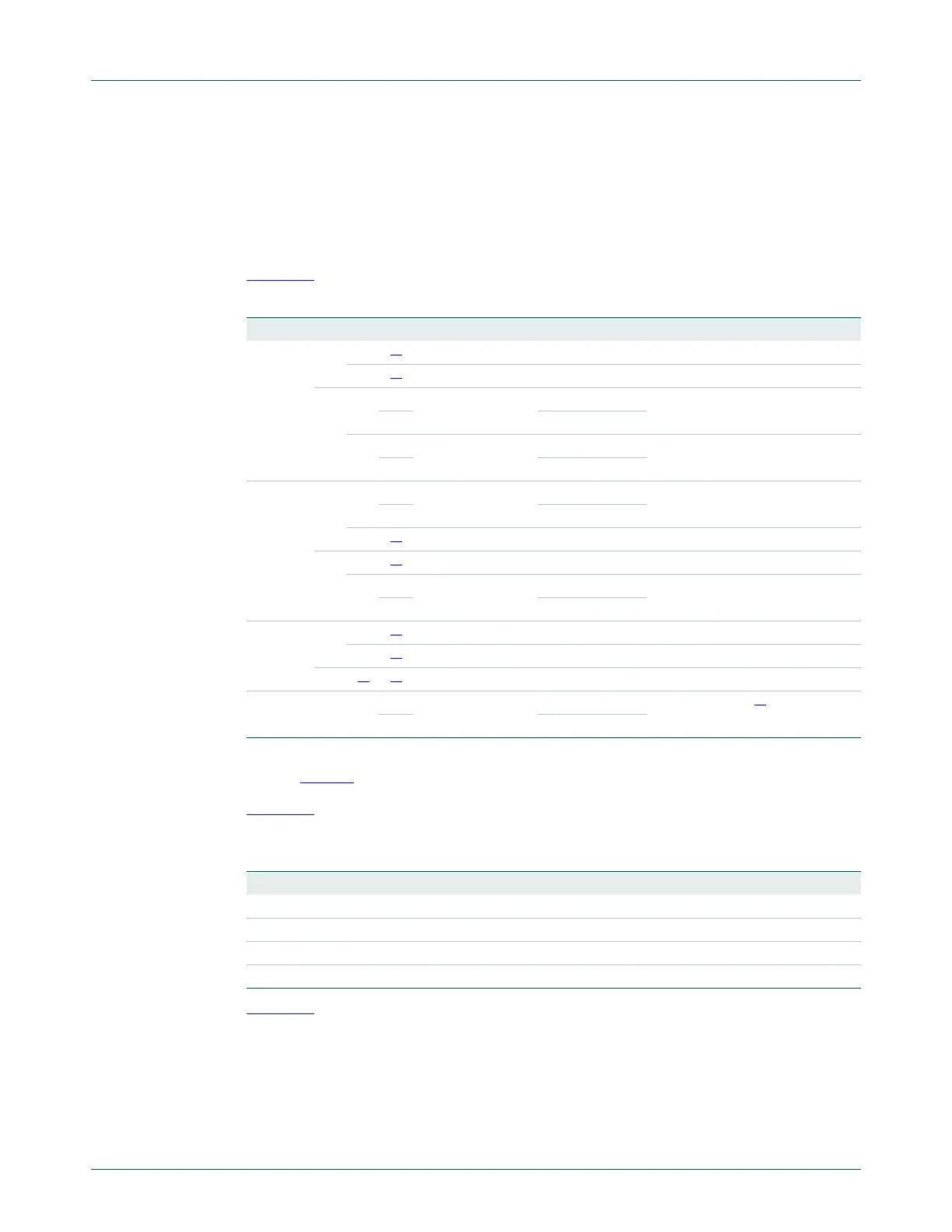

Table 687

shows the encodings for the TEX, C, B, and S access permission bits.

[1] The MPU ignores the value of this bit.

[2] See Table 688

for the encoding of the AA and BB bits.

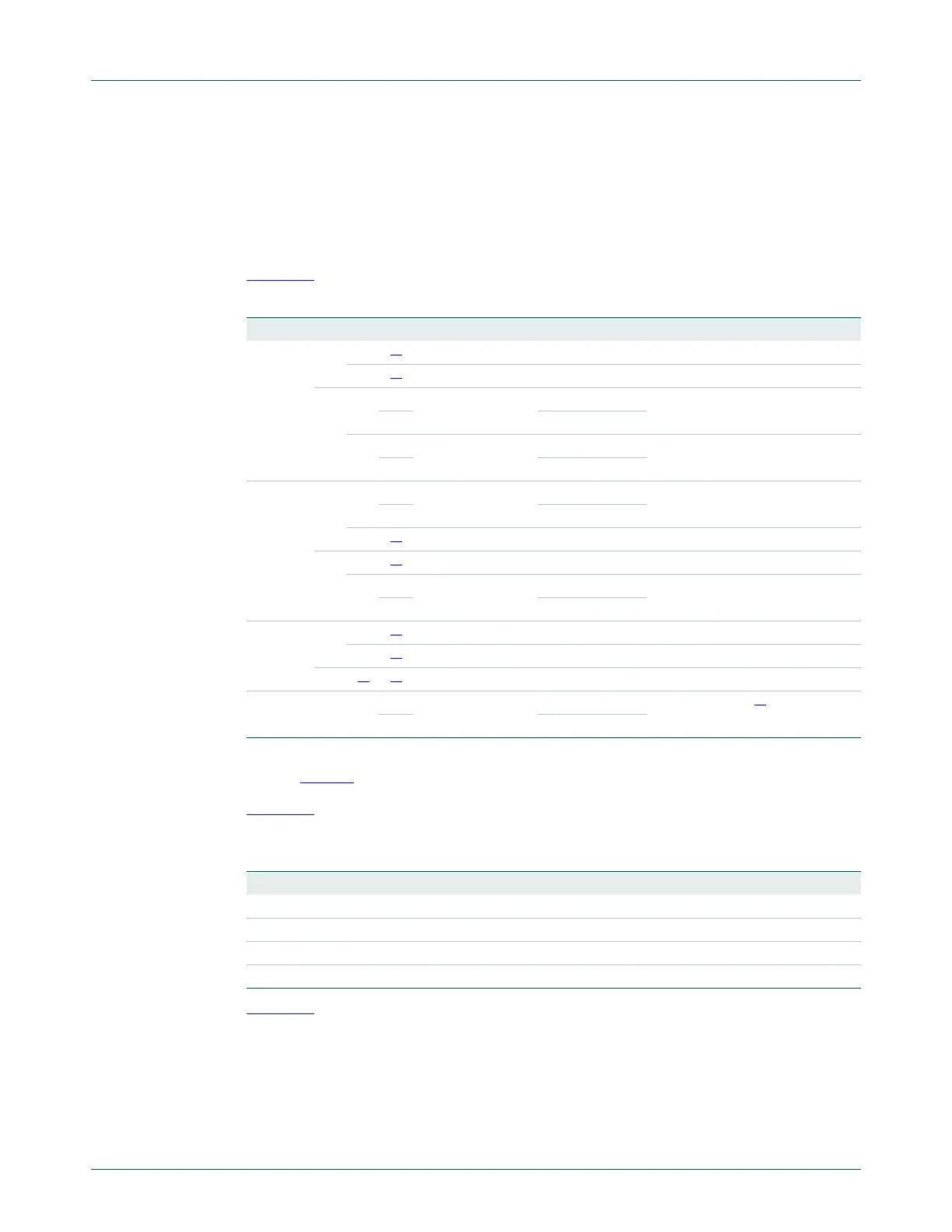

Table 688 shows the cache policy for memory attribute encodings with a TEX value is in

the range 4-7.

Table 689 shows the AP encodings that define the access permissions for privileged and

unprivileged software.

Table 687. TEX, C, B, and S encoding

TEX C B S Memory type Shareability Other attributes

b000 0

0 x

[1]

Strongly-ordered Shareable -

1 x

[1]

Device Shareable -

1 0 0 Normal Not shareable Outer and inner write-through.

No write allocate.

1 Shareable

1 0 Normal Not shareable Outer and inner write-back. No

write allocate.

1 Shareable

b001 0

0 0 Normal Not shareable Outer and inner noncacheable.

1 Shareable

1 x

[1]

Reserved encoding -

1 0 x

[1]

Implementation defined attributes. -

1 0 Normal Not shareable Outer and inner write-back. Write

and read allocate.

1 Shareable

b010 0 0 x

[1]

Device Not shareable Nonshared Device.

1 x

[1]

Reserved encoding -

1x

[1]

x

[1]

Reserved encoding -

b1BB A A 0 Normal Not shareable Cached memory

[2]

, BB = outer

policy, AA = inner policy.

1 Shareable

Table 688. Cache policy for memory attribute encoding

Encoding, AA or BB Corresponding cache policy

00 Non-cacheable

01 Write back, write and read allocate

10 Write through, no write allocate

11 Write back, no write allocate

Loading...

Loading...