UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 56 of 841

NXP Semiconductors

UM10360

Chapter 4: LPC176x/5x Clocking and power control

The CCLK is derived from the PLL0 output signal, divided by CCLKSEL + 1. Having

CCLKSEL = 2 results in CCLK being one third of the PLL0 output, CCLKSEL = 3 results in

CCLK being one quarter of the PLL0 output, etc.

4.7.2 USB Clock Configuration register (USBCLKCFG - 0x400F C108)

This register is used only if the USB PLL (PLL1) is not connected (via the PLLC1 bit in

PLL1CON). If PLL1 is connected, its output is automatically used as the USB clock

source, and PLL1 must be configured to supply the correct 48 MHz clock to the USB

subsystem. If PLL1 is not connected, the USB subsystem will be driven by PLL0 via the

USB clock divider.

The USBCLKCFG register controls the division of the PLL0 output before it is used by the

USB subsystem.The PLL0 output must be divided in order to bring the USB clock

frequency to 48 MHz with a 50% duty cycle. A 4-bit divider allows obtaining the correct

USB clock from any even multiple of 48 MHz (i.e. any multiple of 96 MHz) within the PLL

operating range.

Remark: The Internal RC oscillator should not be used to drive PLL0 when the USB is

using PLL0 as a clock source because a more precise clock is needed for USB

specification compliance (see Table 17

).

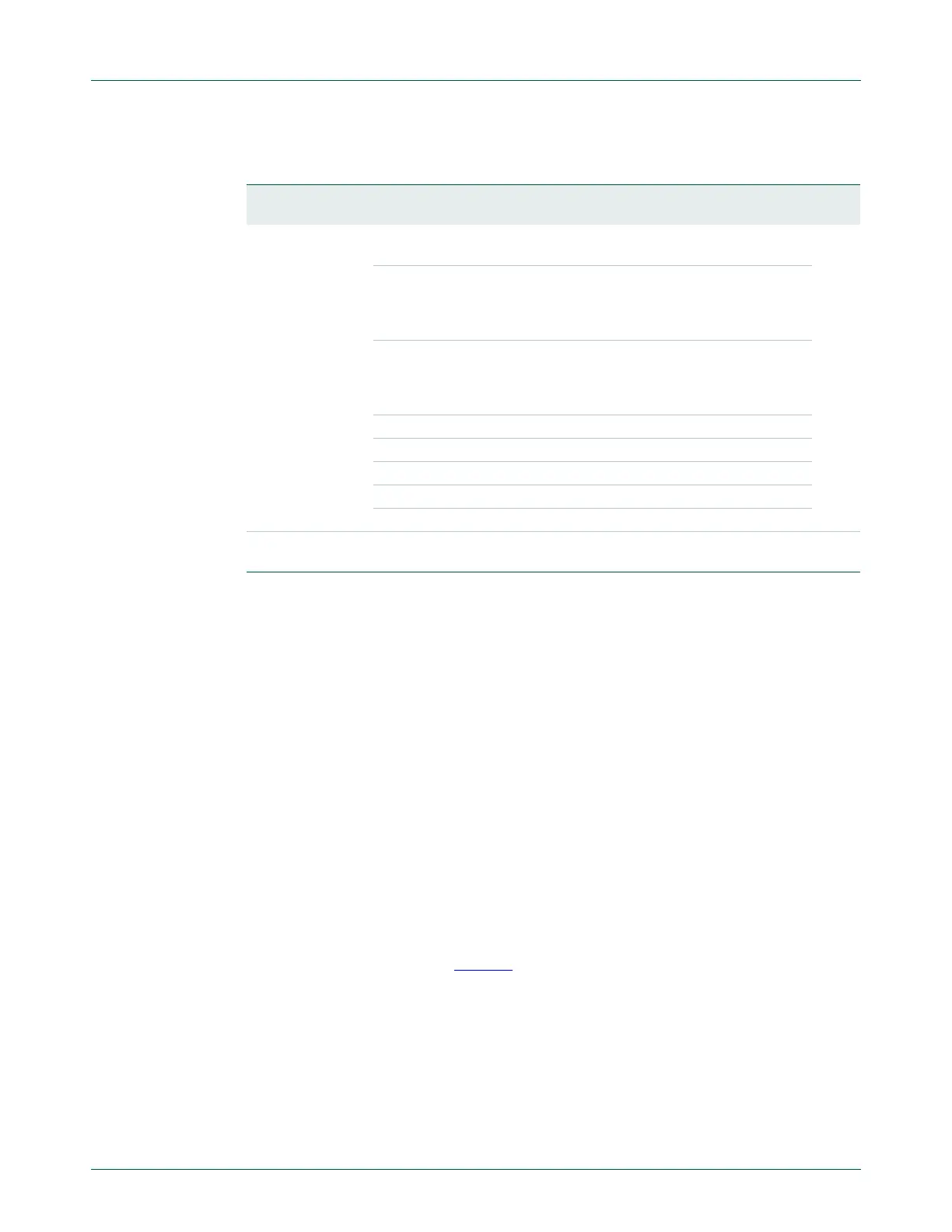

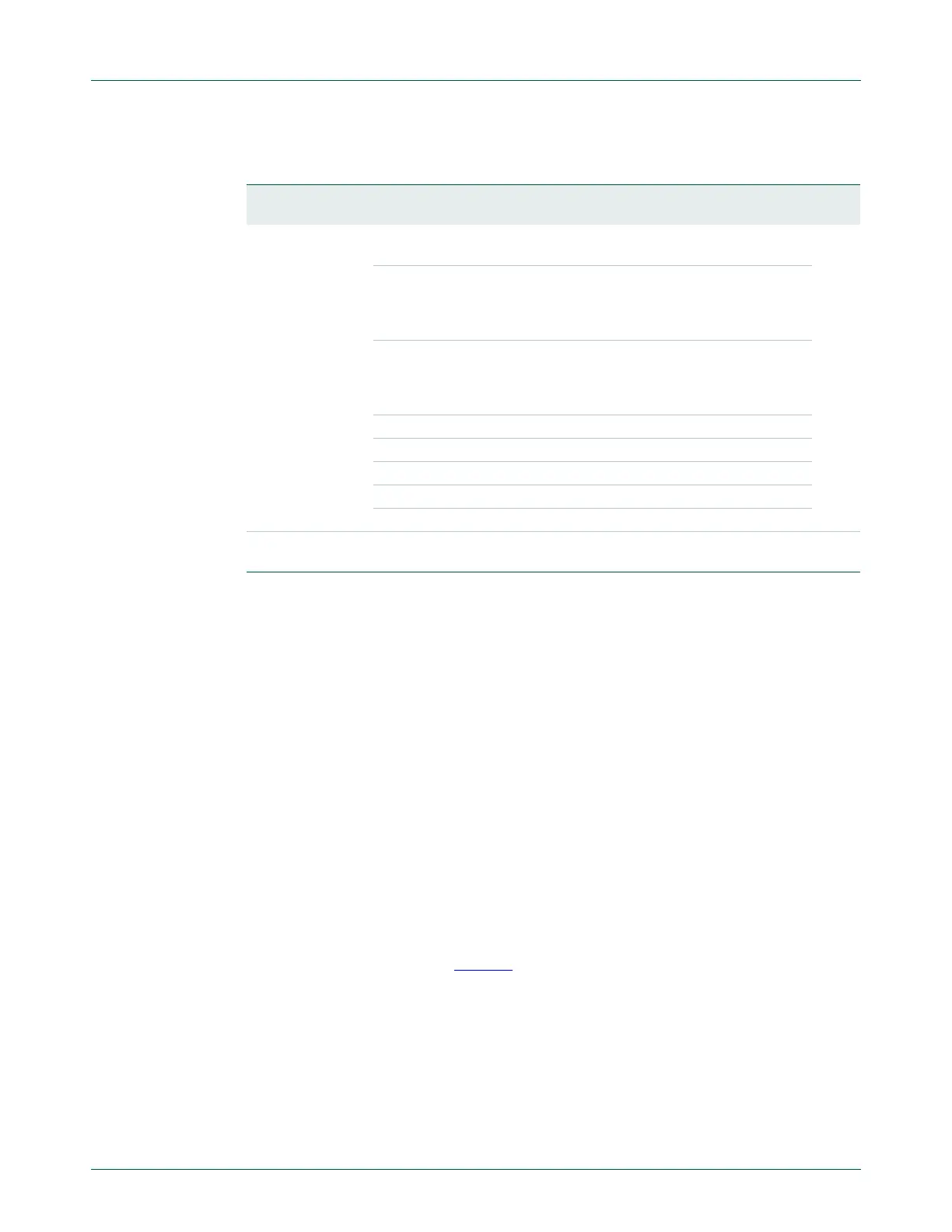

Table 38. CPU Clock Configuration register (CCLKCFG - address 0x400F C104) bit

description

Bit Symbol Value Description Reset

value

7:0 CCLKSEL Selects the divide value for creating the CPU clock (CCLK)

from the PLL0 output.

0x00

0 pllclk is divided by 1 to produce the CPU clock. This setting is

not allowed when the PLL0 is connected, because the rate

would always be greater than the maximum allowed CPU

clock.

1 pllclk is divided by 2 to produce the CPU clock. This setting is

not allowed when the PLL0 is connected, because the rate

would always be greater than the maximum allowed CPU

clock.

2 pllclk is divided by 3 to produce the CPU clock.

3 pllclk is divided by 4 to produce the CPU clock.

4 pllclk is divided by 5 to produce the CPU clock.

::

255 pllclk is divided by 256 to produce the CPU clock.

31:8 - Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

Loading...

Loading...