UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 20 December 2013 778 of 841

NXP Semiconductors

UM10360

Chapter 34: Appendix: Cortex-M3 user guide

34.4.3.11 Configurable Fault Status Register

The CFSR indicates the cause of a memory management fault, bus fault, or usage fault.

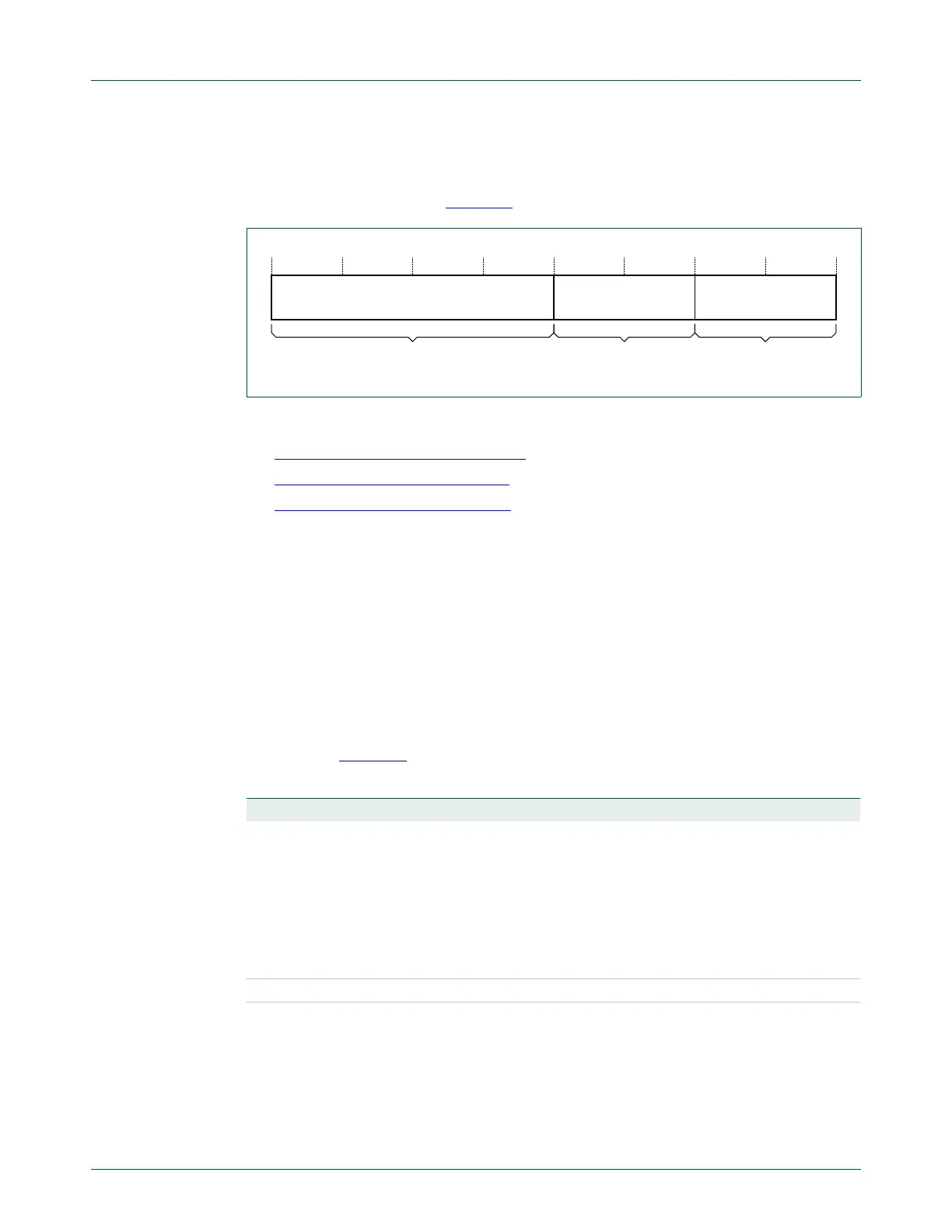

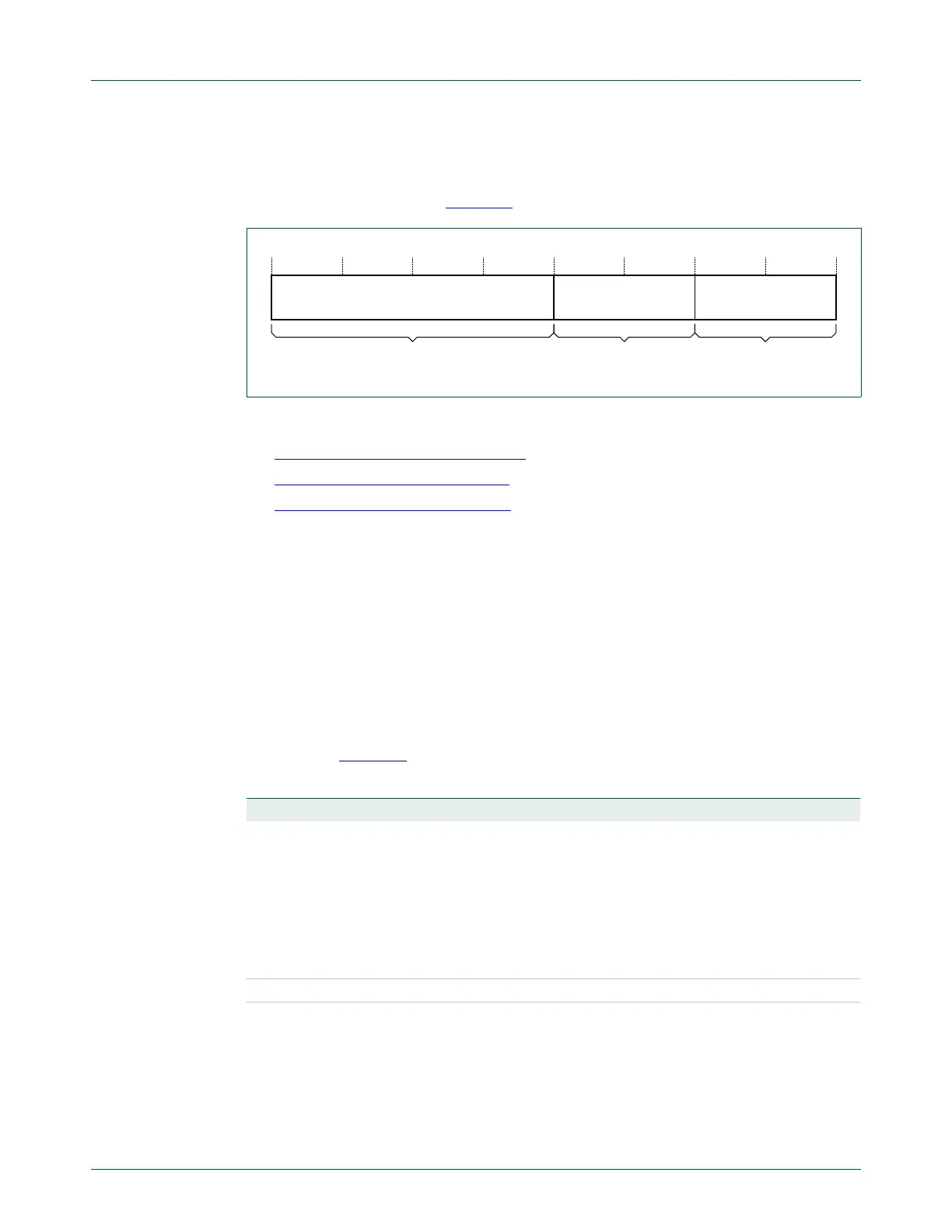

See the register summary in Table 654

for its attributes. The bit assignments are:

The following subsections describe the subregisters that make up the CFSR:

• Table 668 “MMFSR bit assignments”

• Table 673 “BFAR bit assignments”

• Table 670 “UFSR bit assignments”.

The CFSR is byte accessible. You can access the CFSR or its subregisters as follows:

• access the complete CFSR with a word access to

0xE000ED28

• access the MMFSR with a byte access to

0xE000ED28

• access the MMFSR and BFSR with a halfword access to

0xE000ED28

• access the BFSR with a byte access to

0xE000ED29

• access the UFSR with a halfword access to

0xE000ED2A

.

34.4.3.11.1 Memory Management Fault Status Register

The flags in the MMFSR indicate the cause of memory access faults. The bit assignments

are shown in Table 668

.

Fig 149. CFSR bit assignments

0HPRU\0DQDJHPHQW

)DXOW6WDWXV5HJLVWHU

8VDJH)DXOW6WDWXV5HJLVWHU

%XV)DXOW6WDWXV

5HJLVWHU

8)65 %)65 00)65

Table 668. MMFSR bit assignments

Bits Name Function

[7] MMARVALID Memory Management Fault Address Register (MMAR) valid flag:

0 = value in MMAR is not a valid fault address

1 = MMAR holds a valid fault address.

If a memory management fault occurs and is escalated to a hard

fault because of priority, the hard fault handler must set this bit to 0.

This prevents problems on return to a stacked active memory

management fault handler whose MMAR value has been

overwritten.

[6:5] - Reserved.

[4] MSTKERR Memory manager fault on stacking for exception entry:

0 = no stacking fault

1 = stacking for an exception entry has caused one or more access

violations.

When this bit is 1, the SP is still adjusted but the values in the

context area on the stack might be incorrect. The processor has not

written a fault address to the MMAR.

Loading...

Loading...