UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 43 of 841

NXP Semiconductors

UM10360

Chapter 4: LPC176x/5x Clocking and power control

4.5.11 Procedure for determining PLL0 settings

PLL0 parameter determination can be simplified by using a spreadsheet available from

NXP. To determine PLL0 parameters by hand, the following general procedure may be

used:

1. Determine if the application requires use of the USB interface, and whether it will be

clocked from PLL0. The USB requires a 50% duty cycle clock of 48 MHz within a very

small tolerance, which means that F

CCO

must be an even integer multiple of 48 MHz

(i.e. an integer multiple of 96 MHz), within a very small tolerance.

2. Choose the desired processor operating frequency (CCLK). This may be based on

processor throughput requirements, need to support a specific set of UART baud

rates, etc. Bear in mind that peripheral devices may be running from a lower clock

frequency than that of the processor (see Section 4.7 “

Clock dividers” on page 55 and

Section 4.8 “

Power control” on page 59). Find a value for F

CCO

that is close to a

multiple of the desired CCLK frequency, bearing in mind the requirement for USB

support in [1] above, and that lower values of F

CCO

result in lower power dissipation.

3. Choose a value for the PLL input frequency (F

IN

). This can be a clock obtained from

the main oscillator, the RTC oscillator, or the on-chip RC oscillator. For USB support,

the main oscillator should be used. Bear in mind that if PLL1 rather than PLL0 is used

to clock the USB subsystem, this affects the choice of the main oscillator frequency.

4. Calculate values for M and N to produce a sufficiently accurate F

CCO

frequency. The

desired M value -1 will be written to the MSEL0 field in PLL0CFG. The desired N value

-1 will be written to the NSEL0 field in PLL0CFG.

In general, it is better to use a smaller value for N, to reduce the level of multiplication that

must be accomplished by the CCO. Due to the difficulty in finding the best values in some

cases, it is recommended to use a spreadsheet or similar method to show many

possibilities at once, from which an overall best choice may be selected. A spreadsheet is

available from NXP for this purpose.

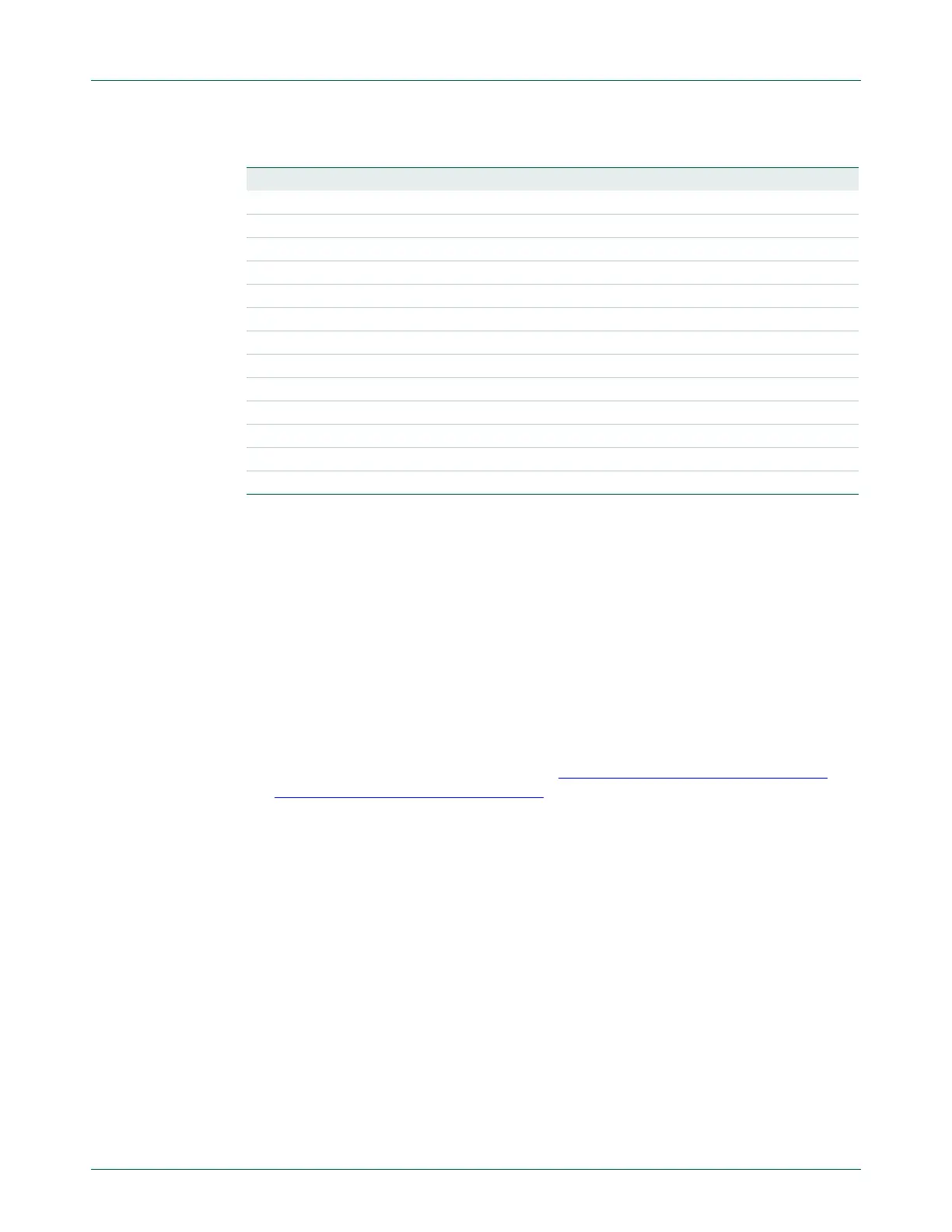

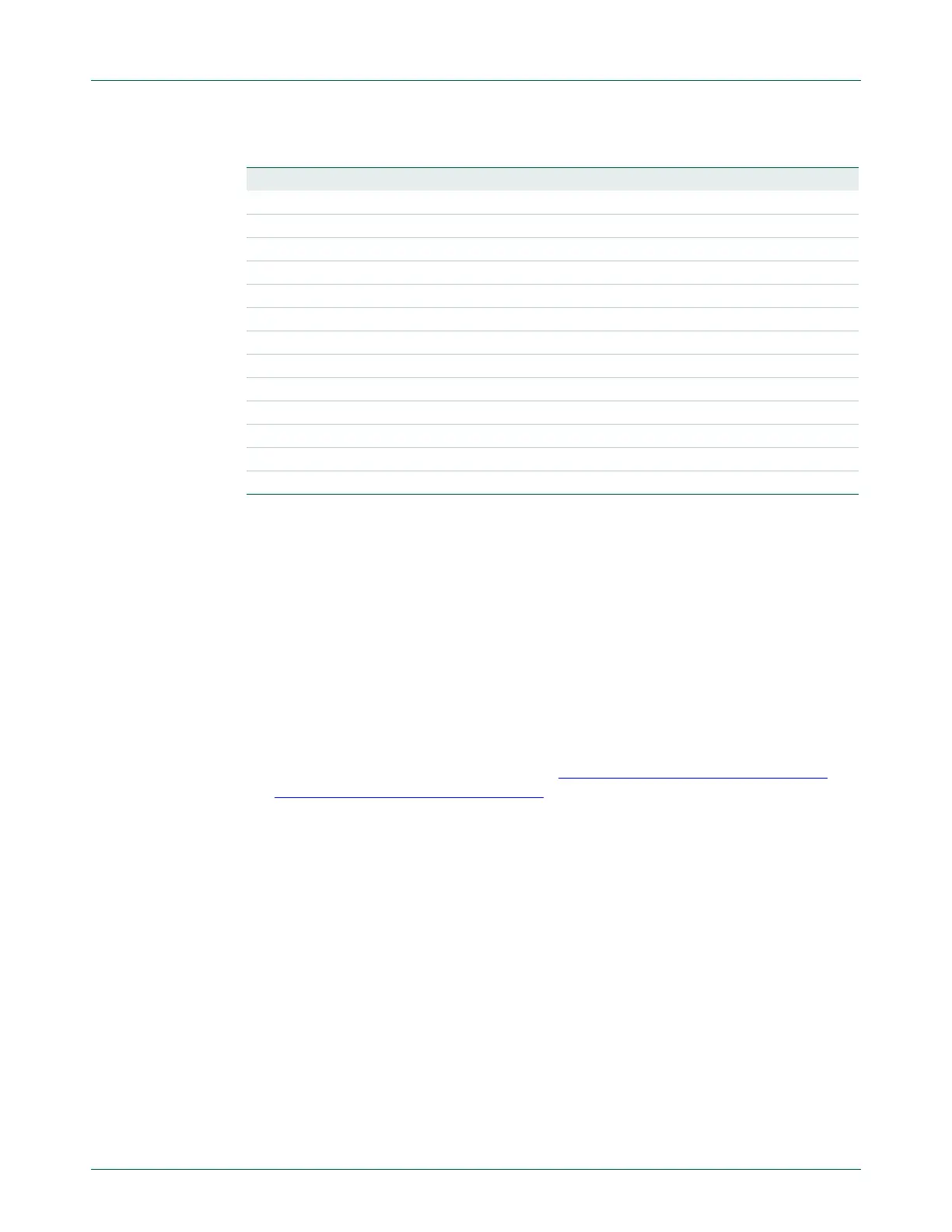

Table 26. Additional Multiplier Values for use with a Low Frequency Clock Input

Low Frequency PLL Multipliers

4272 4395 4578 4725 4807

5127 5188 5400 5493 5859

6042 6075 6104 6409 6592

6750 6836 6866 6958 7050

7324 7425 7690 7813 7935

8057 8100 8545 8789 9155

9613 10254 10376 10986 11719

12085 12207 12817 13184 13672

13733 13916 14099 14420 14648

15381 15564 15625 15869 16113

16479 17578 18127 18311 19226

19775 20508 20599 20874 21149

21973 23071 23438 23804 24170

Loading...

Loading...