UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 171 of 841

NXP Semiconductors

UM10360

Chapter 10: LPC176x/5x Ethernet

The interrupt clear register is write-only. Writing a 1 to a bit of the IntClear register clears

the corresponding bit in the status register. Writing a 0 will not affect the interrupt status.

10.14.4 Interrupt Set Register (IntSet - 0x5000 0FEC)

The Interrupt Set register (IntSet) is a write-only register with an address of 0x5000 0FEC.

The interrupt set register bit definition is shown in Table 173

.

The interrupt set register is write-only. Writing a 1 to a bit of the IntSet register sets the

corresponding bit in the status register. Writing a 0 will not affect the interrupt status.

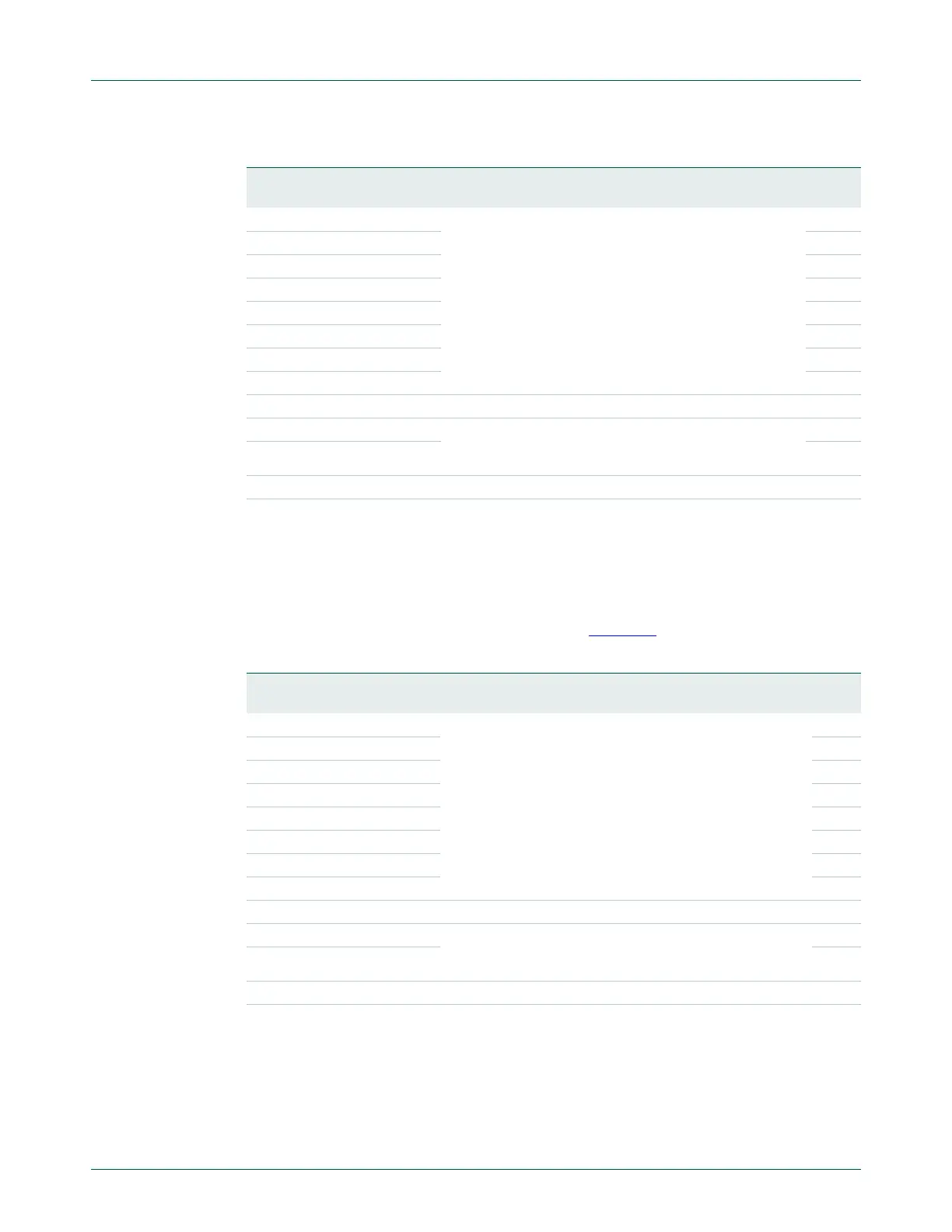

Table 172. Interrupt Clear register (IntClear - address 0x5000 0FE8) bit description

Bit Symbol Function Reset

value

0 RxOverrunIntClr Writing a ’1’ to one of these bits clears (0 to 7) the

corresponding status bit in interrupt status register

IntStatus.

0

1 RxErrorIntClr 0

2 RxFinishedIntClr 0

3 RxDoneIntClr 0

4 TxUnderrunIntClr 0

5 TxErrorIntClr 0

6 TxFinishedIntClr 0

7 TxDoneIntClr 0

11:8 - Unused 0x0

12 SoftIntClr Writing a ’1’ to one of these bits (12 and/or 13) clears the

corresponding status bit in interrupt status register

IntStatus.

0

13 WakeupIntClr 0

31:14 - Unused 0x0

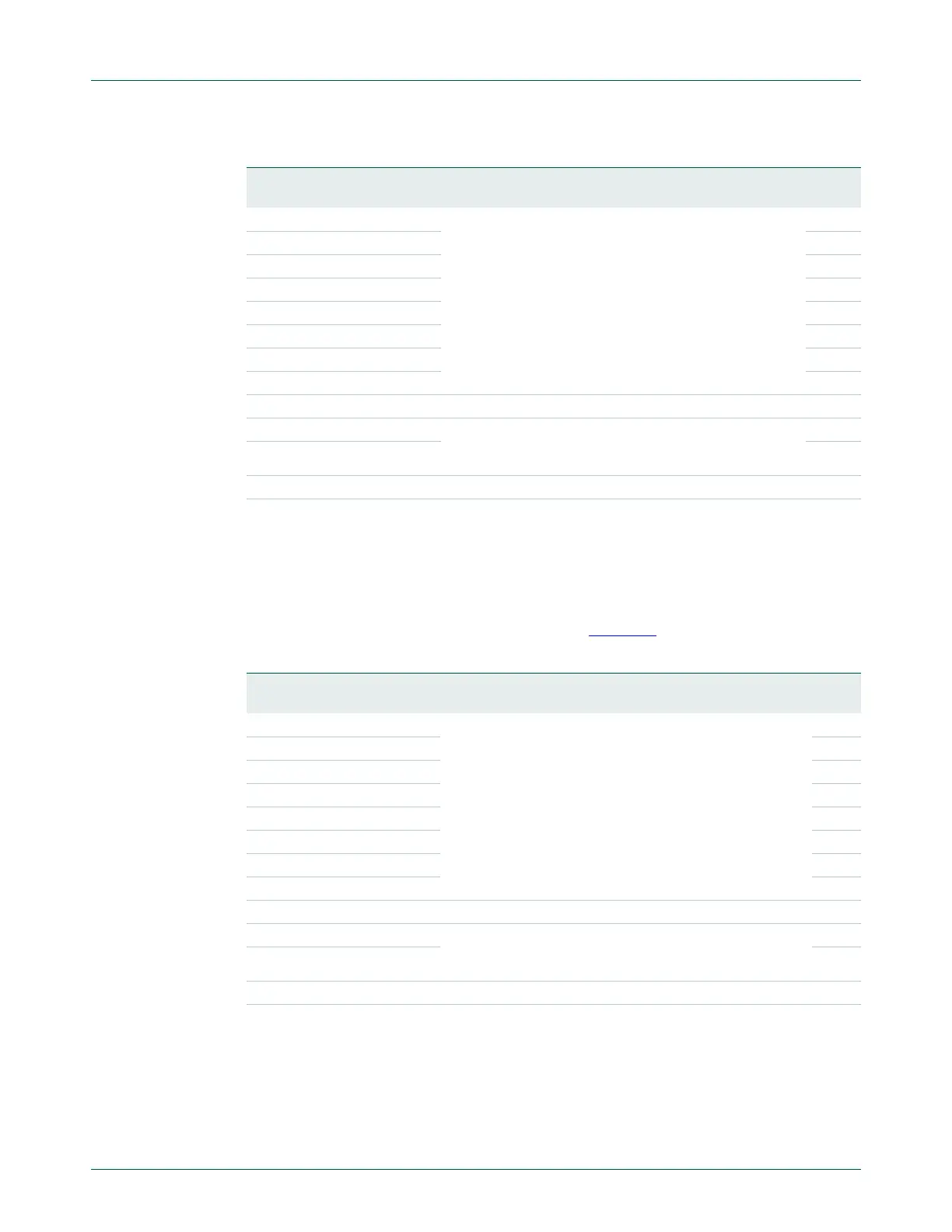

Table 173. Interrupt Set register (IntSet - address 0x5000 0FEC) bit description

Bit Symbol Function Reset

value

0 RxOverrunIntSet Writing a ’1’ to one of these bits (0 to 7) sets the

corresponding status bit in interrupt status register

IntStatus.

0

1 RxErrorIntSet 0

2 RxFinishedIntSet 0

3 RxDoneIntSet 0

4 TxUnderrunIntSet 0

5 TxErrorIntSet 0

6 TxFinishedIntSet 0

7 TxDoneIntSet 0

11:8 - Unused 0x0

12 SoftIntSet Writing a ’1’ to one of these bits (12 and/or 13) sets the

corresponding status bit in interrupt status register

IntStatus.

0

13 WakeupIntSet 0

31:14 - Unused 0x0

Loading...

Loading...