UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 252 of 841

NXP Semiconductors

UM10360

Chapter 11: LPC176x/5x USB device controller

Remark: This command may be invoked by using the USBCmdCode and USBCmdData

registers, or by setting the corresponding bit in USBEpIntClr. For ease of use, using the

USBEpIntClr register is recommended.

11.12.12 Set Endpoint Status (Command: 0x40 - 0x55, Data: write 1 byte

(optional))

The Set Endpoint Status command sets status bits 7:5 and 0 of the endpoint. The

Command Code of Set Endpoint Status is equal to the sum of 0x40 and the physical

endpoint number in hex. Not all bits can be set for all types of endpoints.

11.12.13 Clear Buffer (Command: 0xF2, Data: read 1 byte (optional))

When an OUT packet sent by the host has been received successfully, an internal

hardware FIFO status Buffer_Full flag is set. All subsequent packets will be refused by

returning a NAK. When the device software has read the data, it should free the buffer by

issuing the Clear Buffer command. This clears the internal Buffer_Full flag. When the

buffer is cleared, new packets will be accepted.

When bit 0 of the optional data byte is 1, the previously received packet was over-written

by a SETUP packet. The Packet over-written bit is used only in control transfers.

According to the USB specification, a SETUP packet should be accepted irrespective of

the buffer status. The software should always check the status of the PO bit after reading

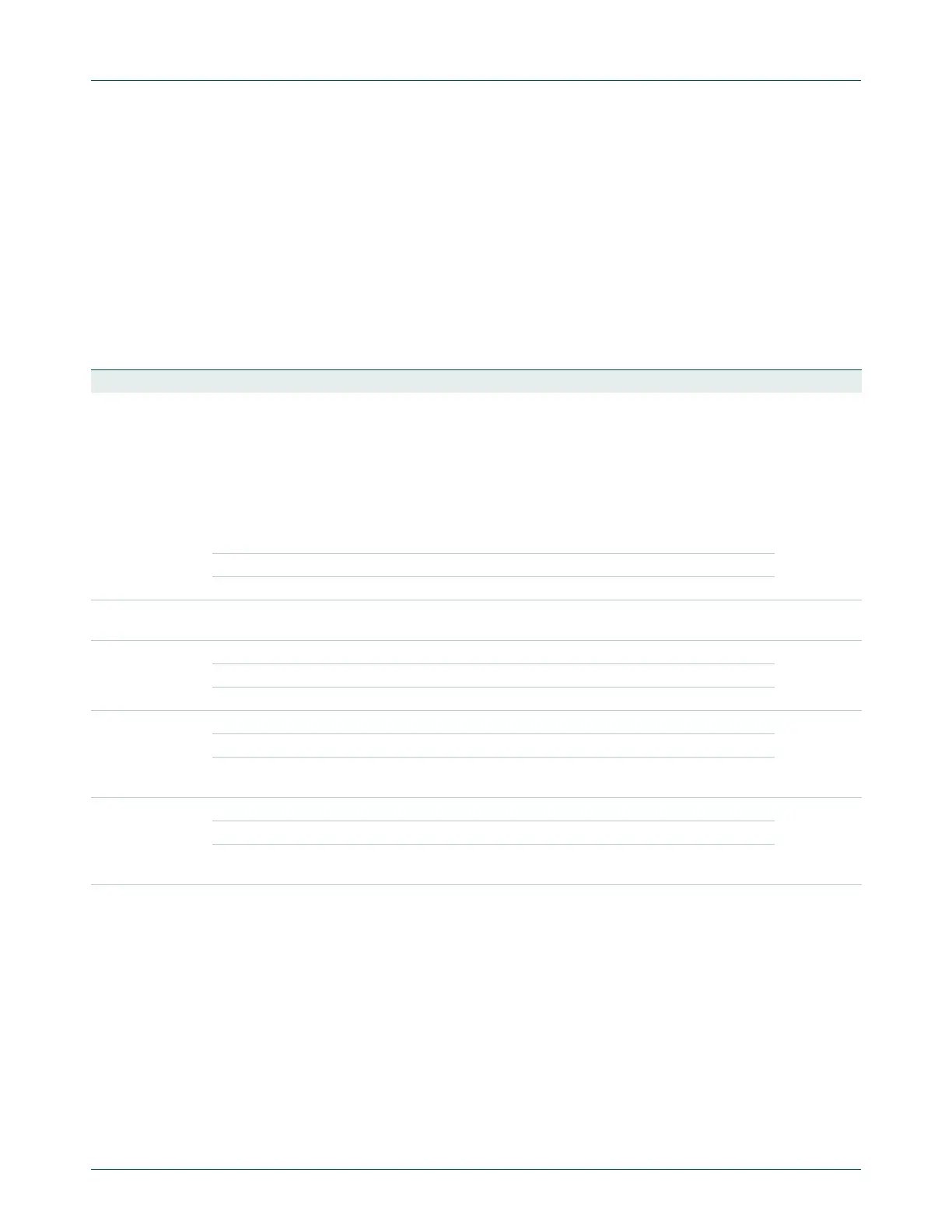

Table 249. Set Endpoint Status command bit description

Bit Symbol Value Description Reset value

0 ST Stalled endpoint bit. A Stalled control endpoint is automatically unstalled when it

receives a SETUP token, regardless of the content of the packet. If the endpoint

should stay in its stalled state, the CPU can stall it again by setting this bit. When

a stalled endpoint is unstalled - either by the Set Endpoint Status command or by

receiving a SETUP token - it is also re-initialized. This flushes the buffer: in case

of an OUT buffer it waits for a DATA 0 PID; in case of an IN buffer it writes a DATA

0 PID. There is no change of the interrupt status of the endpoint. When already

unstalled, writing a zero to this bit initializes the endpoint. When an endpoint is

stalled by the Set Endpoint Status command, it is also re-initialized.

0

0 The endpoint is unstalled.

1 The endpoint is stalled.

4:1 - - Reserved, user software should not write ones to reserved bits. The value read

from a reserved bit is not defined.

NA

5 DA Disabled endpoint bit. 0

0 The endpoint is enabled.

1 The endpoint is disabled.

6 RF_MO Rate Feedback Mode. 0

0 Interrupt endpoint is in the Toggle mode.

1 Interrupt endpoint is in the Rate Feedback mode. This means that transfer takes

place without data toggle bit.

7 CND_ST Conditional Stall bit. 0

0 Unstalls both control endpoints.

1 Stall both control endpoints, unless the STP bit is set in the Select Endpoint

register. It is defined only for control OUT endpoints.

Loading...

Loading...