UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 166 of 841

NXP Semiconductors

UM10360

Chapter 10: LPC176x/5x Ethernet

[1] The EMAC doesn't distinguish the frame type and frame length, so, e.g. when the IP(0x8000) or

ARP(0x0806) packets are received, it compares the frame type with the max length and gives the "Length

out of range" error. In fact, this bit is not an error indication, but simply a statement by the chip regarding the

status of the received frame.

10.12.16 Flow Control Counter Register (FlowControlCounter - 0x5000 0170)

The Flow Control Counter register (FlowControlCounter) has an address of 0x5000 0170.

Table 163

lists the bit definitions of the register.

10.12.17 Flow Control Status Register (FlowControlStatus - 0x5000 0174)

The Flow Control Status register (FlowControlStatus) is a read-only register with an

address of 0x5000 0174. Table 164

lists the bit definitions of the register.

26 Dribble Nibble Indicates that after the end of packet another 1-7 bits were

received. A single nibble, called dribble nibble, is formed

but not sent out.

0

27 Control frame The frame was a control frame. 0

28 PAUSE The frame was a control frame with a valid PAUSE

opcode.

0

29 Unsupported Opcode The current frame was recognized as a Control Frame but

contains an unknown opcode.

0

30 VLAN Frame’s length/type field contained 0x8100 which is the

VLAN protocol identifier.

0

31 - Unused 0x0

Table 162. Receive Status Vector register (RSV - address 0x5000 0160) bit

description …continued

Bit Symbol Function Reset

value

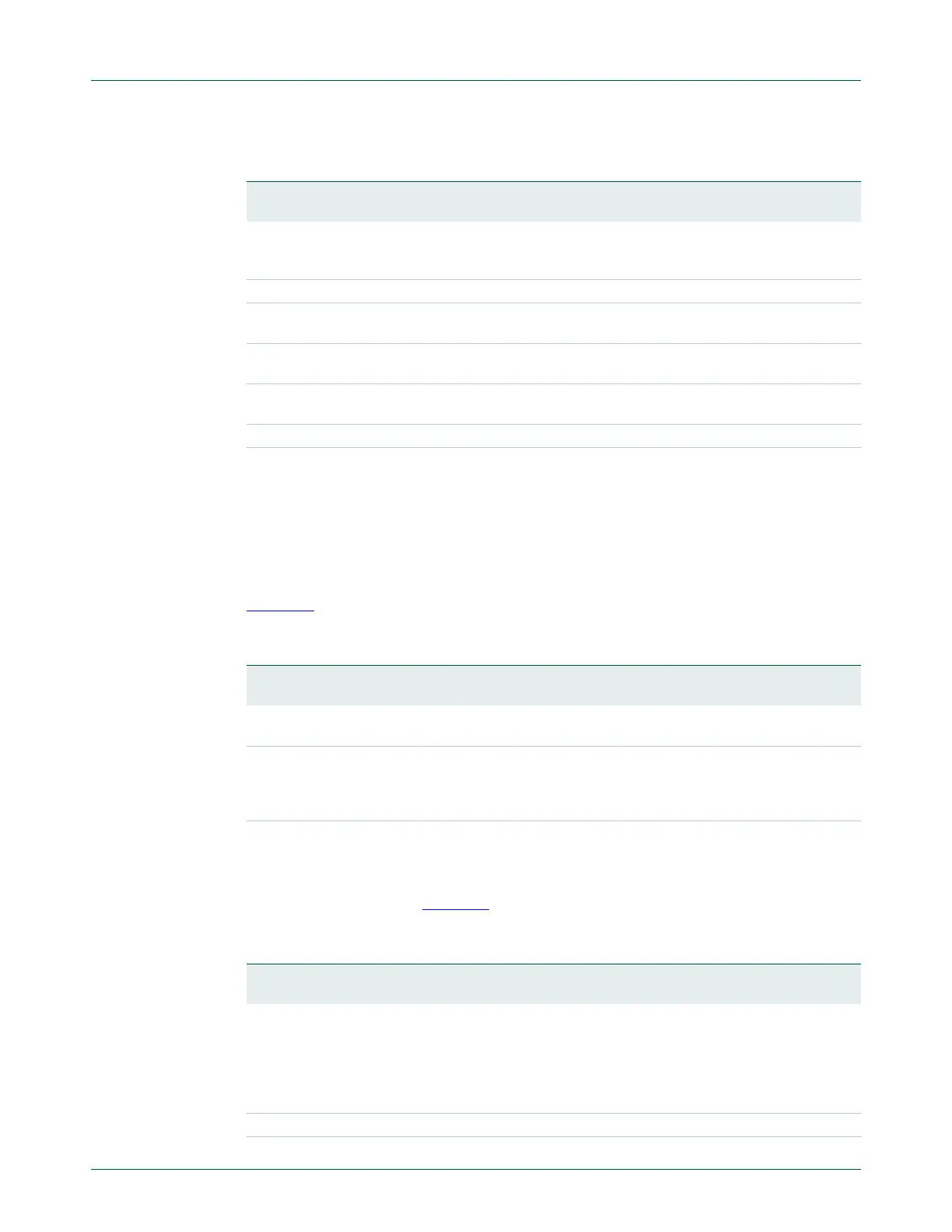

Table 163. Flow Control Counter register (FlowControlCounter - address 0x5000 0170) bit

description

Bit Symbol Function Reset

value

15:0 MirrorCounter In full duplex mode the MirrorCounter specifies the number

of cycles before re-issuing the Pause control frame.

0x0

31:16 PauseTimer In full-duplex mode the PauseTimer specifies the value

that is inserted into the pause timer field of a pause flow

control frame. In half duplex mode the PauseTimer

specifies the number of backpressure cycles.

0x0

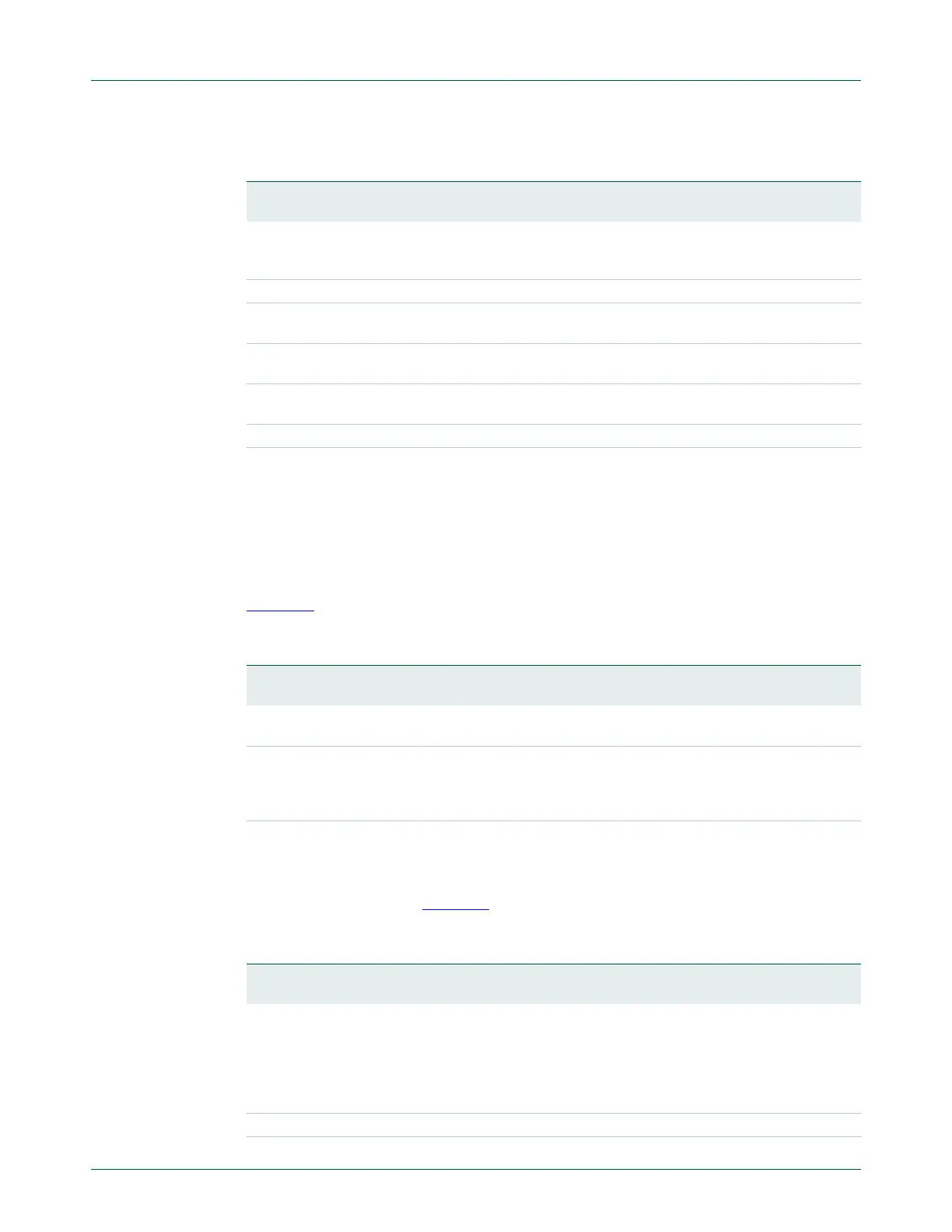

Table 164. Flow Control Status register (FlowControlStatus - address 0x5000 0174) bit

description

Bit Symbol Function Reset

value

15:0 MirrorCounterCurrent In full duplex mode this register represents the current

value of the datapath’s mirror counter which counts up to

the value specified by the MirrorCounter field in the

FlowControlCounter register. In half duplex mode the

register counts until it reaches the value of the PauseTimer

bits in the FlowControlCounter register.

0x0

31:16 - Unused 0x0

Loading...

Loading...