UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 281 of 841

NXP Semiconductors

UM10360

Chapter 13: LPC176x/5x USB OTG

13.8.7 OTG Timer Register (OTGTmr - 0x5000 C114)

13.8.8 OTG Clock Control Register (OTGClkCtrl - 0x5000 CFF4)

This register controls the clocking of the OTG controller. Whenever software wants to

access the registers, the corresponding clock control bit needs to be set. The software

does not have to repeat this exercise for every register access, provided that the

corresponding OTGClkCtrl bits are already set.

8 B_HNP_TRACK Enable HNP tracking for B-device (peripheral), see

Section 13.9

. Hardware clears this bit when

HNP_SUCCESS or HNP_FAILURE is set.

0

9 A_HNP_TRACK Enable HNP tracking for A-device (host), see

Section 13.9

. Hardware clears this bit when

HNP_SUCCESS or HNP_FAILURE is set.

0

10 PU_REMOVED When the B-device changes its role from peripheral to

host, software sets this bit when it removes the D+

pull-up, see Section 13.9

. Hardware clears this bit when

HNP_SUCCESS or HNP_FAILURE is set.

0

15:11 - Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

31:16 TMR_CNT Current timer count value. 0x0

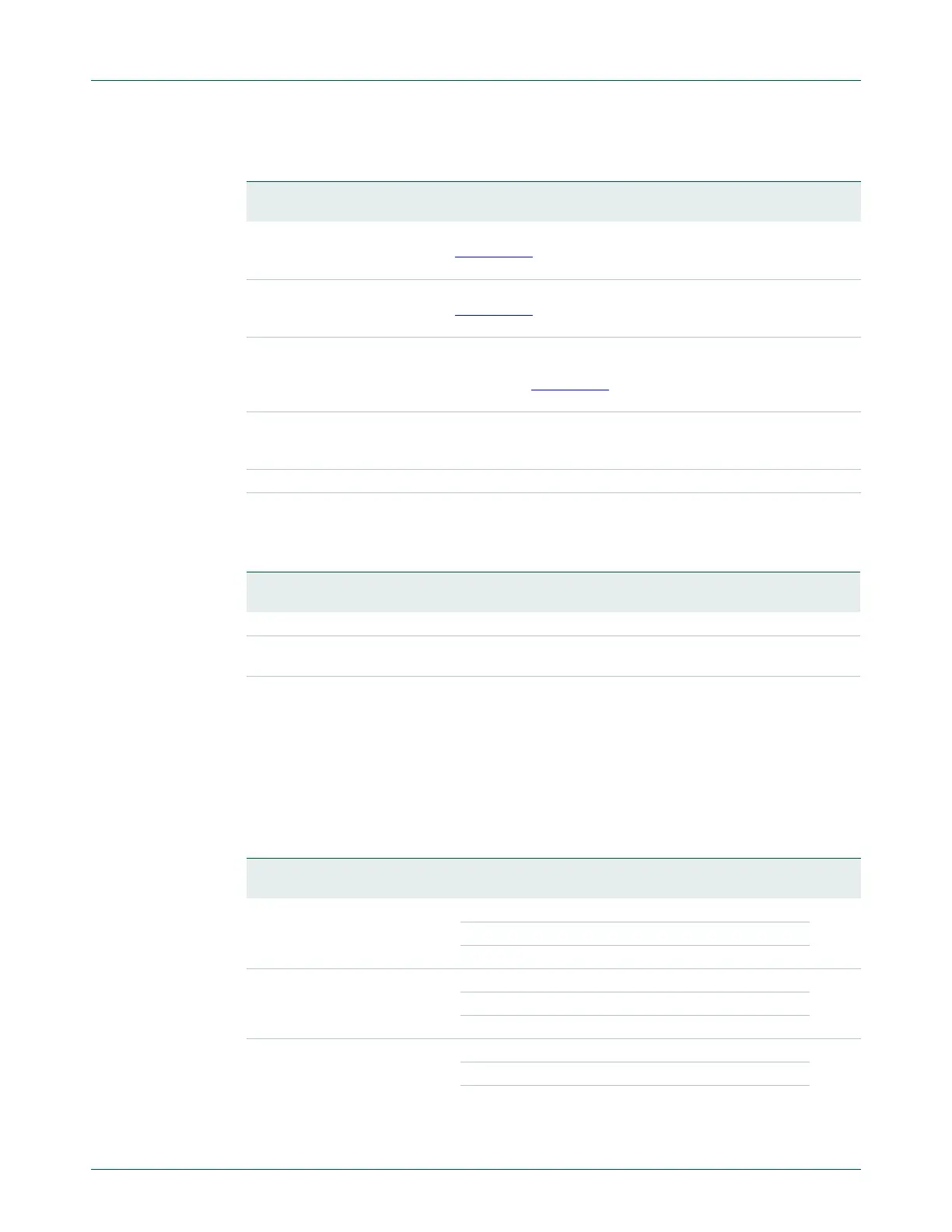

Table 259. OTG Status Control register (OTGStCtrl - address 0x5000 C110) bit

description …continued

Bit Symbol Description Reset

Value

Table 260. OTG Timer register (OTGTmr - address 0x5000 C114) bit description

Bit Symbol Description Reset

Value

15:0 TIMEOUT_CNT The TMR interrupt is set when TMR_CNT reaches this value. 0xFFFF

31:16 - Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

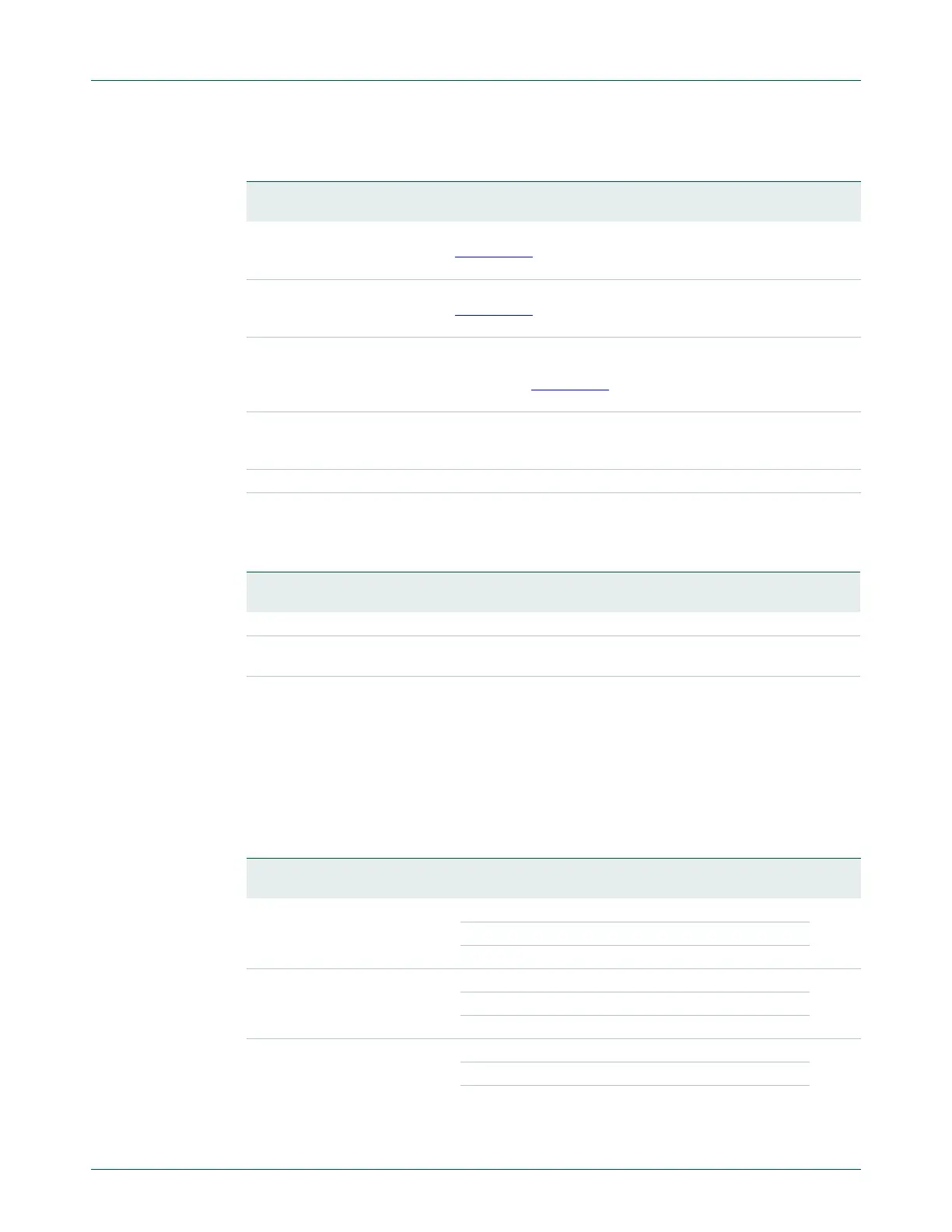

Table 261. OTG clock control register (OTG_clock_control - address 0x5000 CFF4) bit

description

Bit Symbol Value Description Reset

Value

0 HOST_CLK_EN Host clock enable 0

0 Disable the Host clock.

1 Enable the Host clock.

1 DEV_CLK_EN Device clock enable 0

0 Disable the Device clock.

1 Enable the Device clock.

2 I2C_CLK_EN I

2

C clock enable 0

0 Disable the I

2

C clock.

1 Enable the I

2

C clock.

Loading...

Loading...