UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 316 of 841

NXP Semiconductors

UM10360

Chapter 14: LPC176x/5x UART0/2/3

14.4.12.1.1 Example 1: PCLK = 14.7456 MHz, BR = 9600

According to the provided algorithm DL

est

= PCLK/(16 x BR) = 14.7456 MHz / (16 x 9600)

= 96. Since this DL

est

is an integer number, DIVADDVAL = 0, MULVAL = 1, DLM = 0, and

DLL = 96.

14.4.12.1.2 Example 2: PCLK = 12 MHz, BR = 115200

According to the provided algorithm DL

est

= PCLK/(16 x BR) = 12 MHz / (16 x 115200) =

6.51. This DL

est

is not an integer number and the next step is to estimate the FR

parameter. Using an initial estimate of FR

est

= 1.5 a new DL

est

= 4 is calculated and FR

est

is recalculated as FR

est

= 1.628. Since FRest = 1.628 is within the specified range of 1.1

and 1.9, DIVADDVAL and MULVAL values can be obtained from the attached look-up

table.

The closest value for FRest = 1.628 in the look-up Table 286

is FR = 1.625. It is

equivalent to DIVADDVAL = 5 and MULVAL = 8.

Based on these findings, the suggested UART setup would be: DLM = 0, DLL = 4,

DIVADDVAL = 5, and MULVAL = 8. According to Equation 4

the UART rate is 115384.

This rate has a relative error of 0.16% from the originally specified 115200.

14.4.13 UARTn Transmit Enable Register (U0TER - 0x4000 C030, U2TER -

0x4009 8030, U3TER - 0x4009 C030)

The UnTER register enables implementation of software flow control. When TXEn=1,

UARTn transmitter will keep sending data as long as they are available. As soon as TXEn

becomes 0, UARTn transmission will stop.

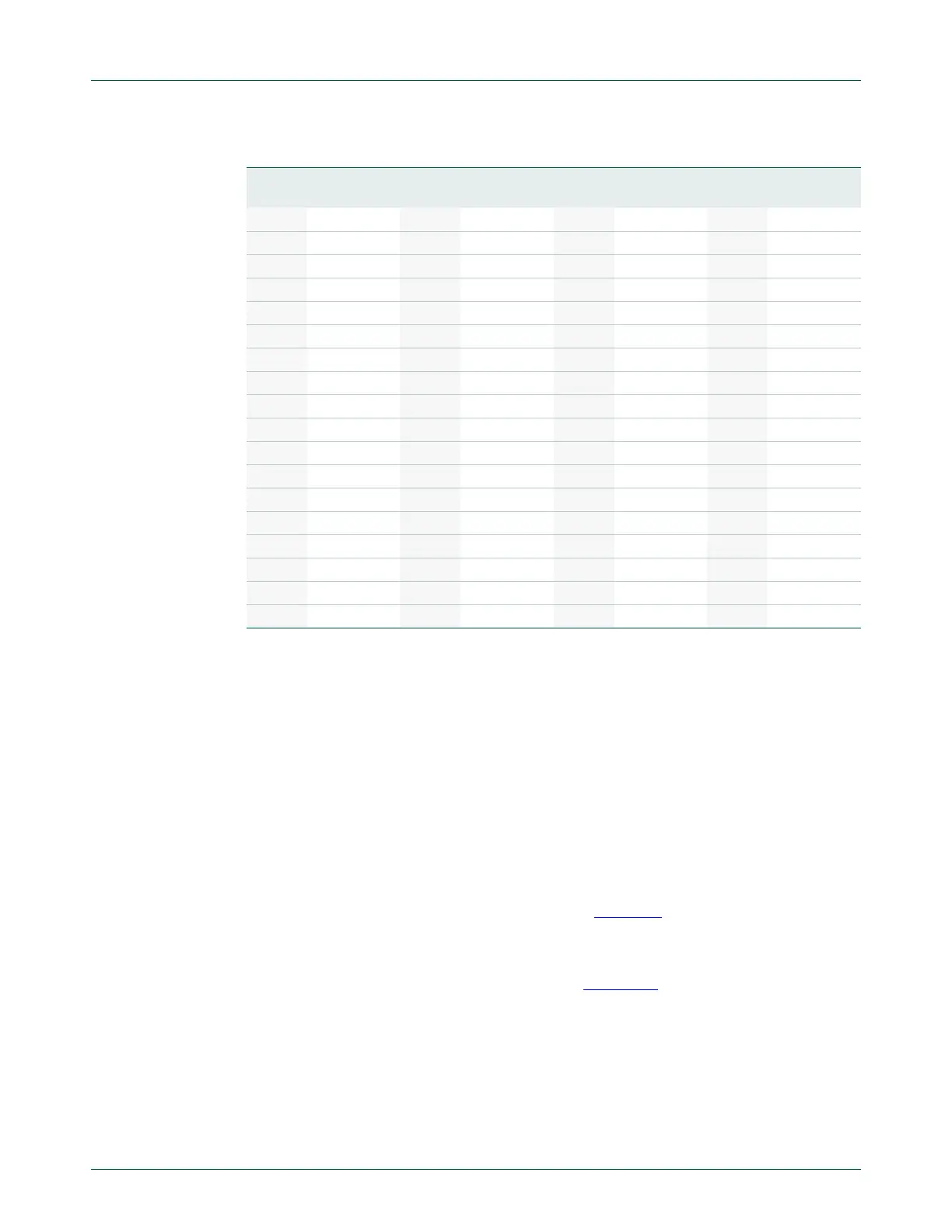

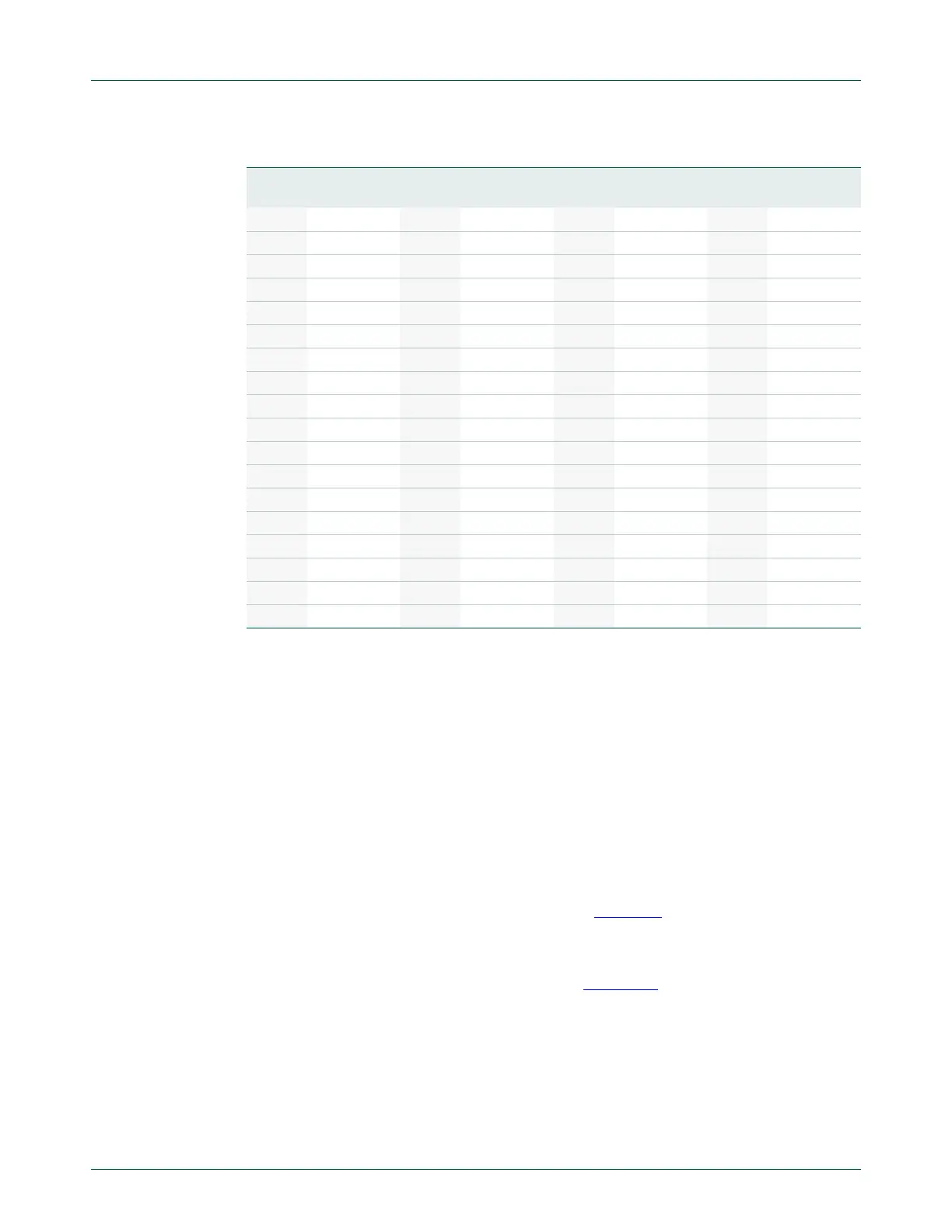

Table 286. Fractional Divider setting look-up table

FR DivAddVal/

MulVal

FR DivAddVal/

MulVal

FR DivAddVal/

MulVal

FR DivAddVal/

MulVal

1.000 0/1 1.250 1/4 1.500 1/2 1.750 3/4

1.067 1/15 1.267 4/15 1.533 8/15 1.769 10/13

1.071 1/14 1.273 3/11 1.538 7/13 1.778 7/9

1.077 1/13 1.286 2/7 1.545 6/11 1.786 11/14

1.083 1/12 1.300 3/10 1.556 5/9 1.800 4/5

1.091 1/11 1.308 4/13 1.571 4/7 1.818 9/11

1.100 1/10 1.333 1/3 1.583 7/12 1.833 5/6

1.111 1/9 1.357 5/14 1.600 3/5 1.846 11/13

1.125 1/8 1.364 4/11 1.615 8/13 1.857 6/7

1.133 2/15 1.375 3/8 1.625 5/8 1.867 13/15

1.143 1/7 1.385 5/13 1.636 7/11 1.875 7/8

1.154 2/13 1.400 2/5 1.643 9/14 1.889 8/9

1.167 1/6 1.417 5/12 1.667 2/3 1.900 9/10

1.182 2/11 1.429 3/7 1.692 9/13 1.909 10/11

1.200 1/5 1.444 4/9 1.700 7/10 1.917 11/12

1.214 3/14 1.455 5/11 1.714 5/7 1.923 12/13

1.222 2/9 1.462 6/13 1.727 8/11 1.929 13/14

1.231 3/13 1.467 7/15 1.733 11/15 1.933 14/15

Loading...

Loading...