UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 448 of 841

NXP Semiconductors

UM10360

Chapter 19: LPC176x/5x I2C0/1/2

19.8.8 I

2

C Mask registers (I2MASK0 to 3: I

2

C0, I2C0MASK[0, 1, 2, 3] -

0x4001 C0[30, 34, 38, 3C]; I

2

C1, I2C1MASK[0, 1, 2, 3] - address

0x4005 C0[30, 34, 38, 3C]; I

2

C2, I2C2MASK[0, 1, 2, 3] - address

0x400A 00[30, 34, 38, 3C])

The four mask registers each contain seven active bits (7:1). Any bit in these registers

which is set to ‘1’ will cause an automatic compare on the corresponding bit of the

received address when it is compared to the I2ADRn register associated with that mask

register. In other words, bits in an I2ADRn register which are masked are not taken into

account in determining an address match.

The mask register has no effect on comparison to the General Call address (“0000000”).

When an address-match interrupt occurs, the processor will have to read the data register

(I2DAT) to determine which received address actually caused the match.

19.8.9 I

2

C SCL HIGH duty cycle register (I2SCLH: I

2

C0, I2C0SCLH -

0x4001 C010; I

2

C1, I2C1SCLH - 0x4005 C010; I

2

C2, I2C2SCLH -

0x400A 0010)

19.8.10 I

2

C SCL Low duty cycle register (I2SCLL: I

2

C0 - I2C0SCLL:

0x4001 C014; I

2

C1 - I2C1SCLL: 0x4005 C014; I

2

C2 - I2C2SCLL:

0x400A 0014)

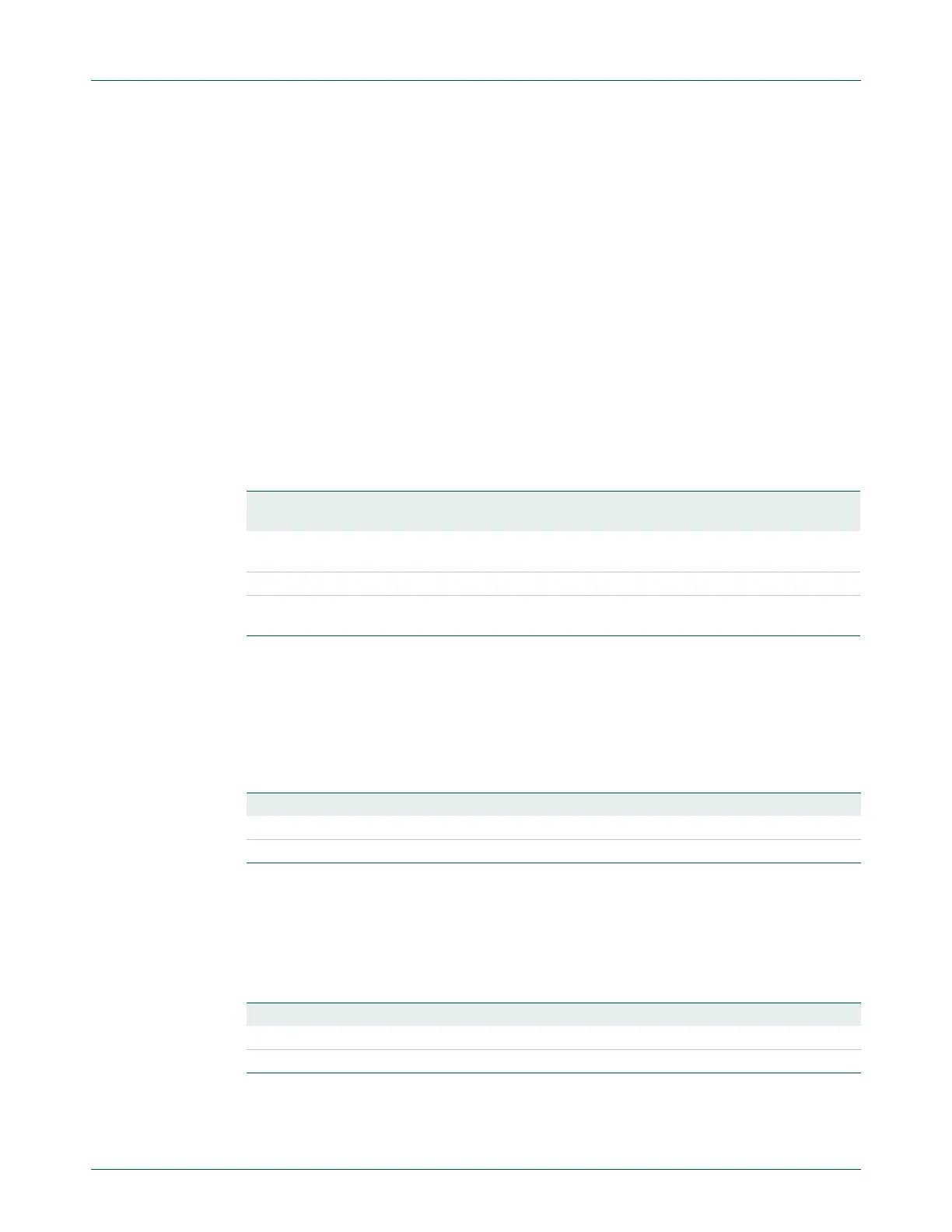

Table 391. I

2

C Mask registers (I2MASK0 to 3: I

2

C0, I2C0MASK[0, 1, 2, 3] - 0x4001 C0[30, 34,

38, 3C]; I

2

C1, I2C1MASK[0, 1, 2, 3] - address 0x4005 C0[30, 34, 38, 3C]; I

2

C2,

I2C2MASK[0, 1, 2, 3] - address 0x400A 00[30, 34, 38, 3C]) bit description

Bit Symbol Description Reset

value

0 - Reserved. User software should not write ones to reserved bits. This bit

reads always back as 0.

0

7:1 MASK Mask bits. 0x00

31:8 - Reserved. User software should not write ones to reserved bits. These

bits read always back as zeroes.

0

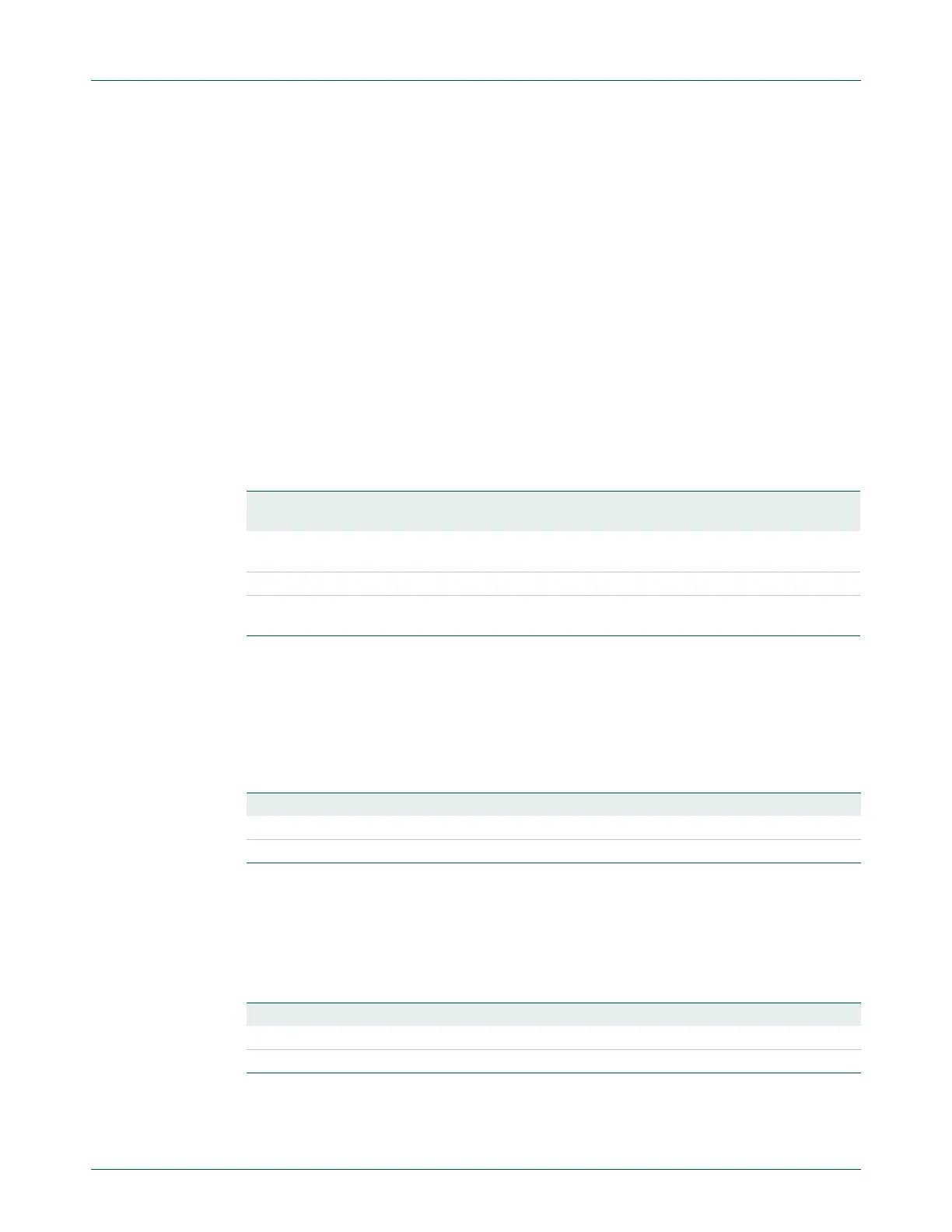

Table 392. I

2

C SCL HIGH Duty Cycle register (I2SCLH: I

2

C0, I2C0SCLH - address

0x4001 C010; I

2

C1, I2C1SCLH - address 0x4005 C010; I

2

C2, I2C2SCLH -

0x400A 0010) bit description

Bit Symbol Description Reset value

15:0 SCLH Count for SCL HIGH time period selection. 0x0004

31:16 - Reserved. The value read from a reserved bit is not defined. NA

Table 393. I

2

C SCL Low duty cycle register (I2SCLL: I

2

C0 - I2C0SCLL: 0x4001 C014; I

2

C1 -

I2C1SCLL: 0x4005 C014; I

2

C2 - I2C2SCLL: 0x400A 0014) bit description

Bit Symbol Description Reset value

15:0 SCLL Count for SCL low time period selection. 0x0004

31:16 - Reserved. The value read from a reserved bit is not defined. NA

Loading...

Loading...