UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 20 December 2013 788 of 841

NXP Semiconductors

UM10360

Chapter 34: Appendix: Cortex-M3 user guide

Use the MPU registers to define the MPU regions and their attributes. The MPU registers

are:

34.4.5.1 MPU Type Register

The TYPE register indicates whether the MPU is present, and if so, how many regions it

supports. See the register summary in Table 680

for its attributes. The bit assignments are

shown in Table 681

.

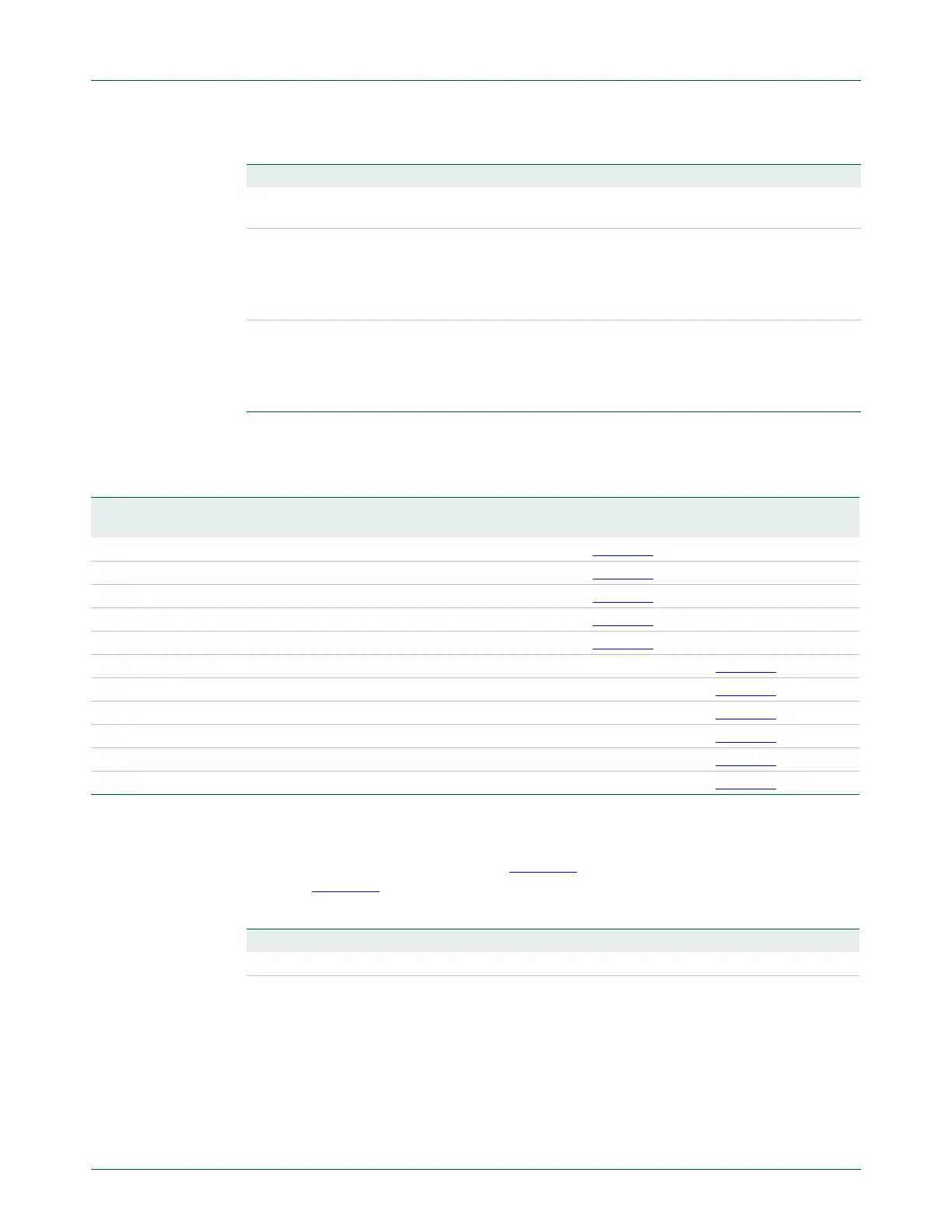

Non-shared - Memory-mapped peripherals that only

a single processor uses.

Normal Shared Non-cacheable

Write-through

Cacheable

Write-back

Cacheable

Normal memory that is shared

between several processors.

Non-shared Non-cacheable

Write-through

Cacheable

Write-back

Cacheable

Normal memory that only a single

processor uses.

Table 679. Memory attributes summary …continued

Memory type Shareability Other attributes Description

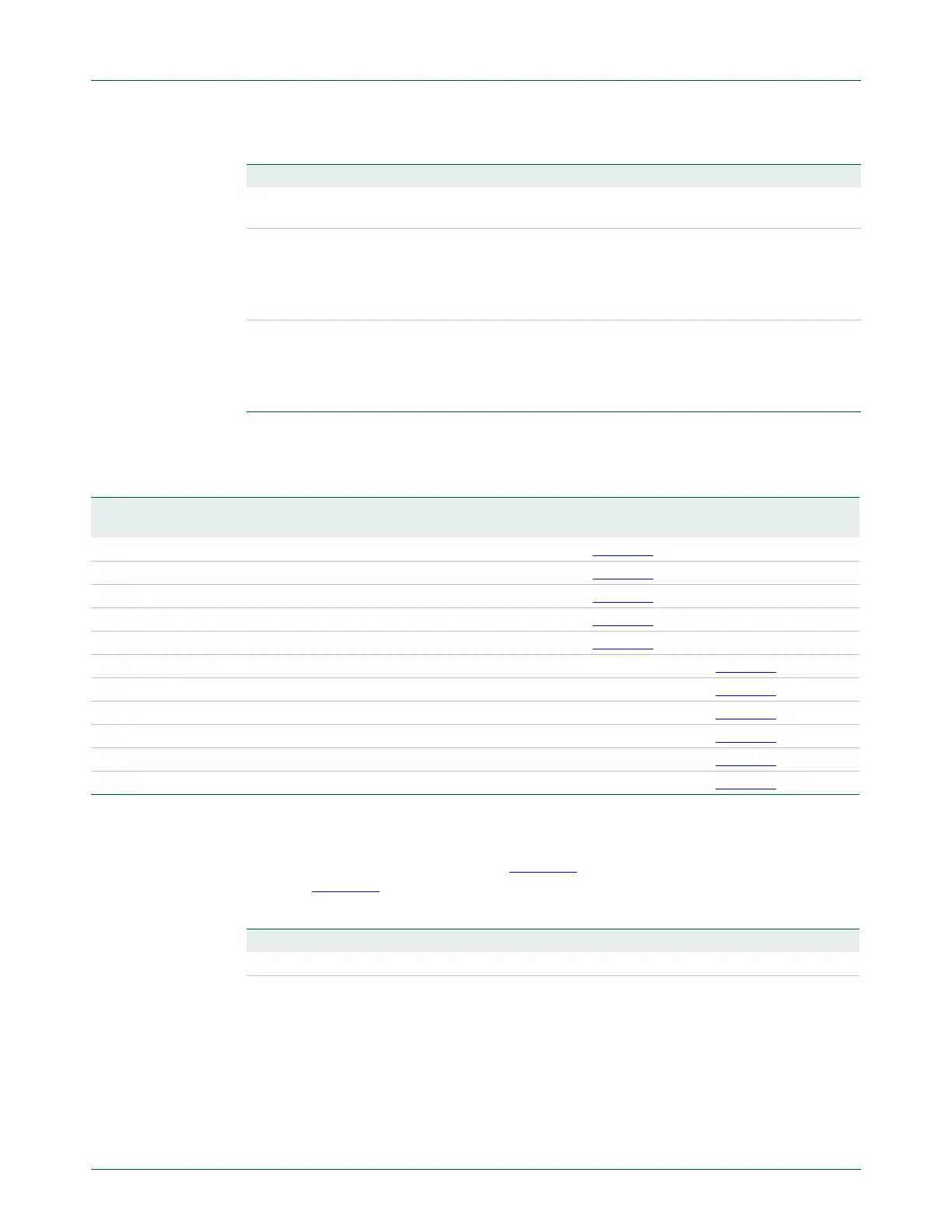

Table 680. MPU registers summary

Address Name Type Required

privilege

Reset

value

Description

0xE000ED90

TYPE RO Privileged

0x00000800

Table 681

0xE000ED94

CTRL RW Privileged

0x00000000

Table 682

0xE000ED98

RNR RW Privileged

0x00000000

Table 683

0xE000ED9C

RBAR RW Privileged

0x00000000

Table 684

0xE000EDA0

RASR RW Privileged

0x00000000

Table 685

0xE000EDA4

RBAR_A1 RW Privileged

0x00000000

Alias of RBAR, see Table 684

0xE000EDA8

RASR_A1 RW Privileged

0x00000000

Alias of RASR, see Table 685

0xE000EDAC

RBAR_A2 RW Privileged

0x00000000

Alias of RBAR, see Table 684

0xE000EDB0

RASR_A2 RW Privileged

0x00000000

Alias of RASR, see Table 685

0xE000EDB4

RBAR_A3 RW Privileged

0x00000000

Alias of RBAR, see Table 684

0xE000EDB8

RASR_A3 RW Privileged

0x00000000

Alias of RASR, see Table 685

Table 681. TYPE register bit assignments

Bits Name Function

[31:24] - Reserved.

[23:16] IREGION Indicates the number of supported MPU instruction

regions.

Always contains

0x00

. The MPU memory map is unified

and is described by the DREGION field.

Loading...

Loading...