UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 20 December 2013 743 of 841

NXP Semiconductors

UM10360

Chapter 34: Appendix: Cortex-M3 user guide

34.3.2.6 Memory endianness

The processor views memory as a linear collection of bytes numbered in ascending order

from zero. For example, bytes 0-3 hold the first stored word, and bytes 4-7 hold the

second stored word. Section 34.3.2.6.1

describes how words of data are stored in

memory.

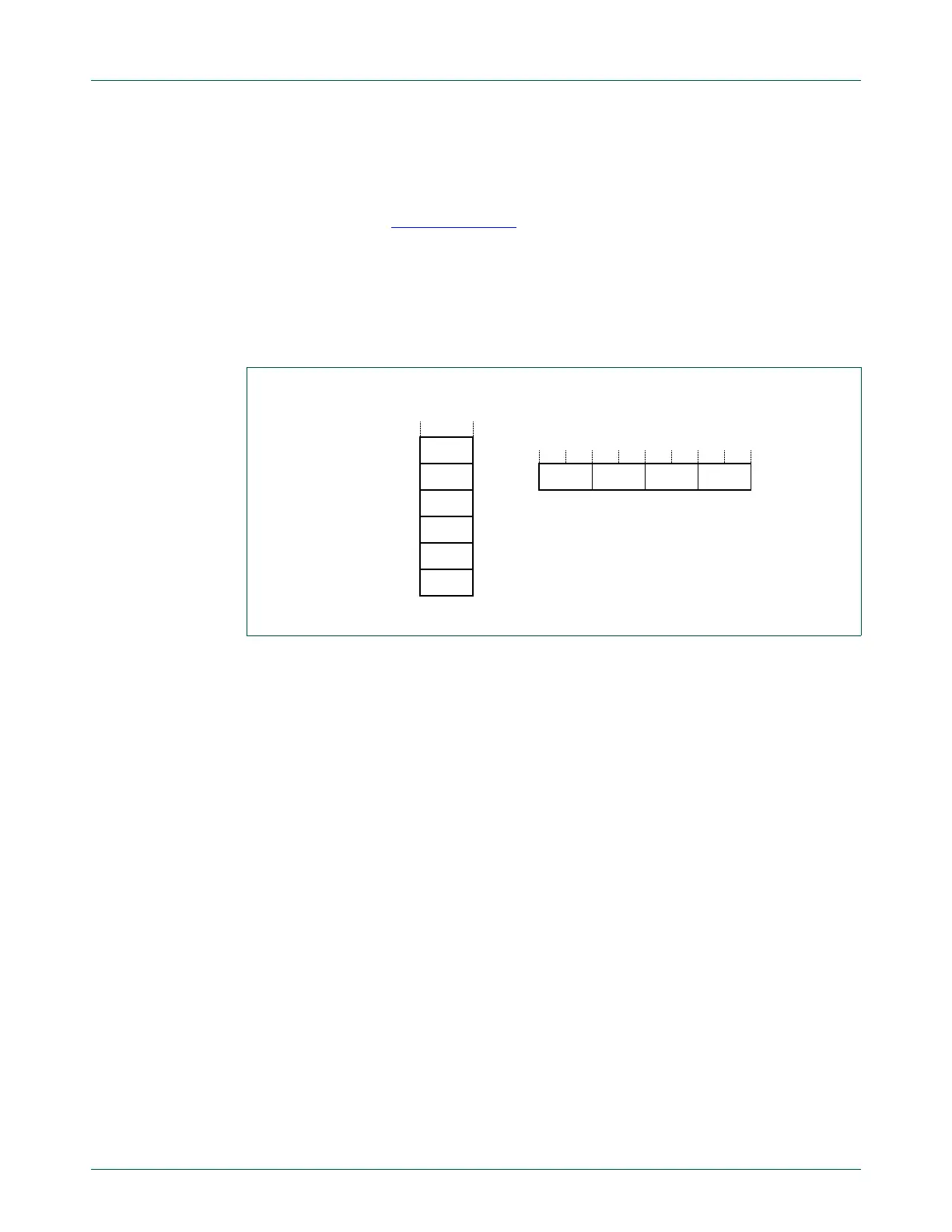

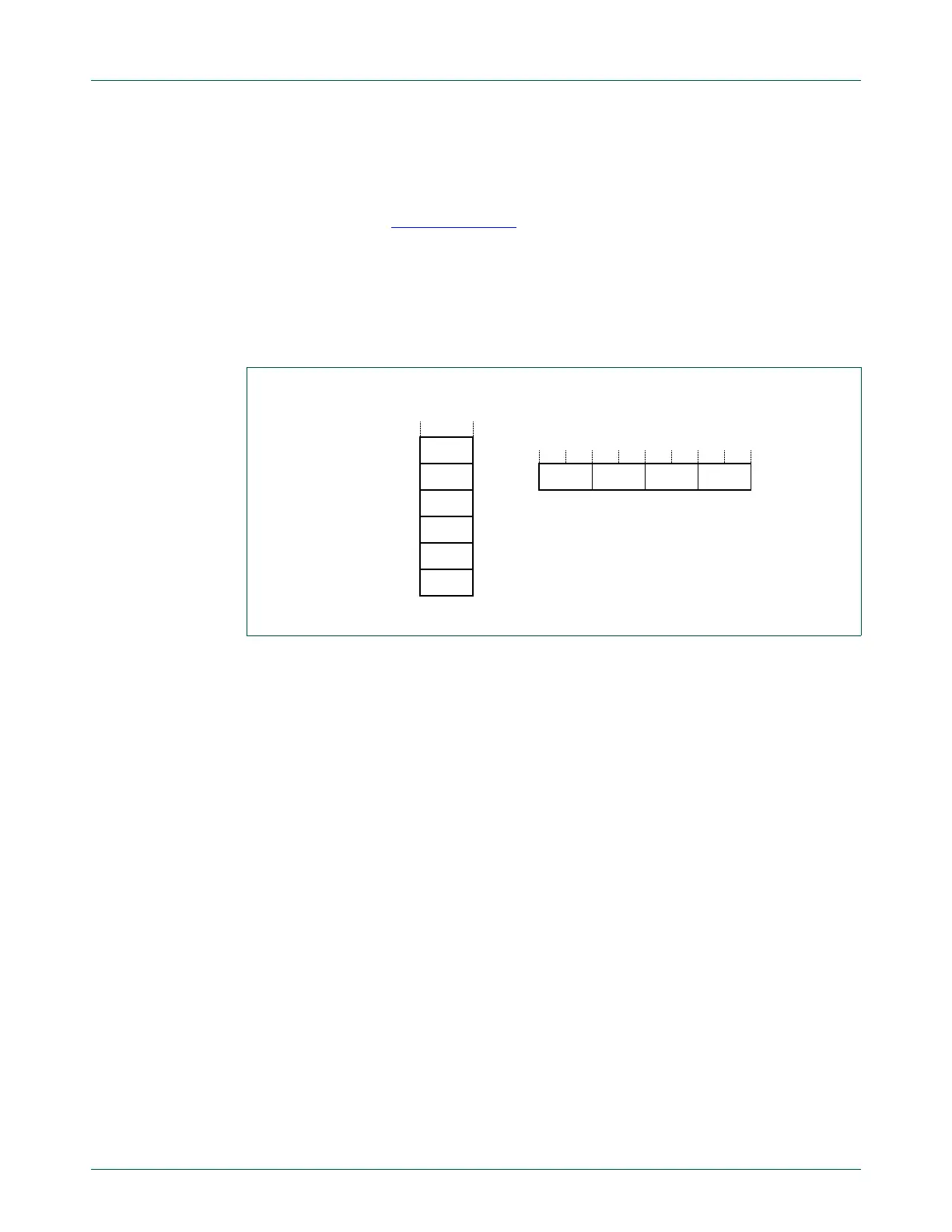

34.3.2.6.1 Little-endian format

In little-endian format, the processor stores the least significant byte of a word at the

lowest-numbered byte, and the most significant byte at the highest-numbered byte. For

example:

34.3.2.7 Synchronization primitives

The Cortex-M3 instruction set includes pairs of synchronization primitives. These

provide a non-blocking mechanism that a thread or process can use to obtain exclusive

access to a memory location. Software can use them to perform a guaranteed

read-modify-write memory update sequence, or for a semaphore mechanism.

A pair of synchronization primitives comprises:

• A Load-Exclusive instruction

Used to read the value of a memory location, requesting exclusive access to that

location.

• A Store-Exclusive instruction

Used to attempt to write to the same memory location, returning a status bit to a

register. If this bit is:

– 0: it indicates that the thread or process gained exclusive access to the memory,

and the write succeeds,

– 1: it indicates that the thread or process did not gain exclusive access to the

memory, and no write is performed,

The pairs of Load-Exclusive and Store-Exclusive instructions are:

• the word instructions

LDREX

and

STREX

• the halfword instructions

LDREXH

and

STREXH

• the byte instructions

LDREXB

and

STREXB

.

Fig 147. Little-endian format

0HPRU\ 5HJLVWHU

$GGUHVV$

$

OVE\WH

PVE\WH

$

$

%%% %

%

%

%

%

Loading...

Loading...