UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 112 of 841

NXP Semiconductors

UM10360

Chapter 8: LPC176x/5x Pin connect block

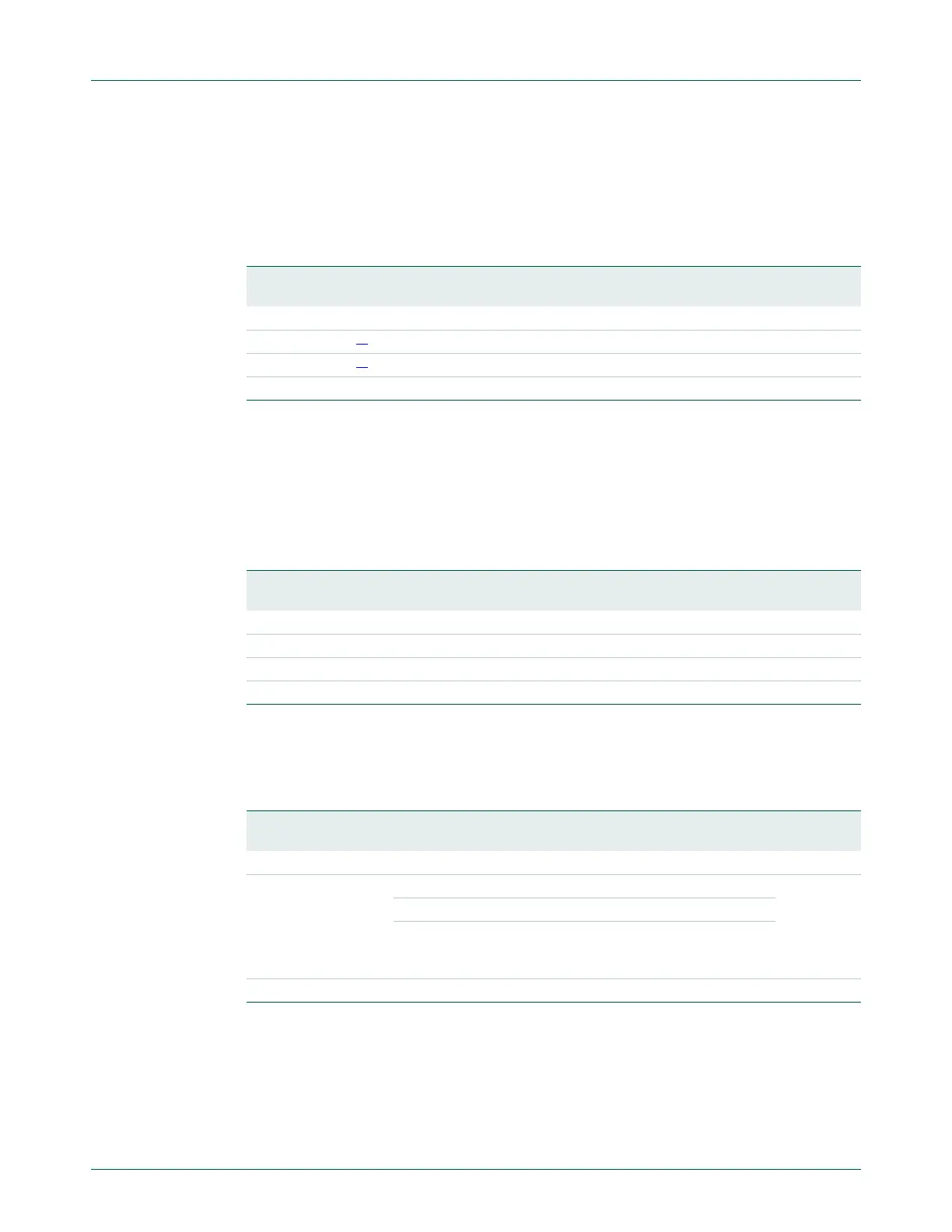

8.5.6 Pin Function Select Register 7 (PINSEL7 - 0x4002 C01C)

The PINSEL7 register controls the functions of the upper half of Port 3. The direction

control bit in the FIO3DIR register is effective only when the GPIO function is selected for

a pin. For other functions, direction is controlled automatically.

[1] Not available on 80-pin package.

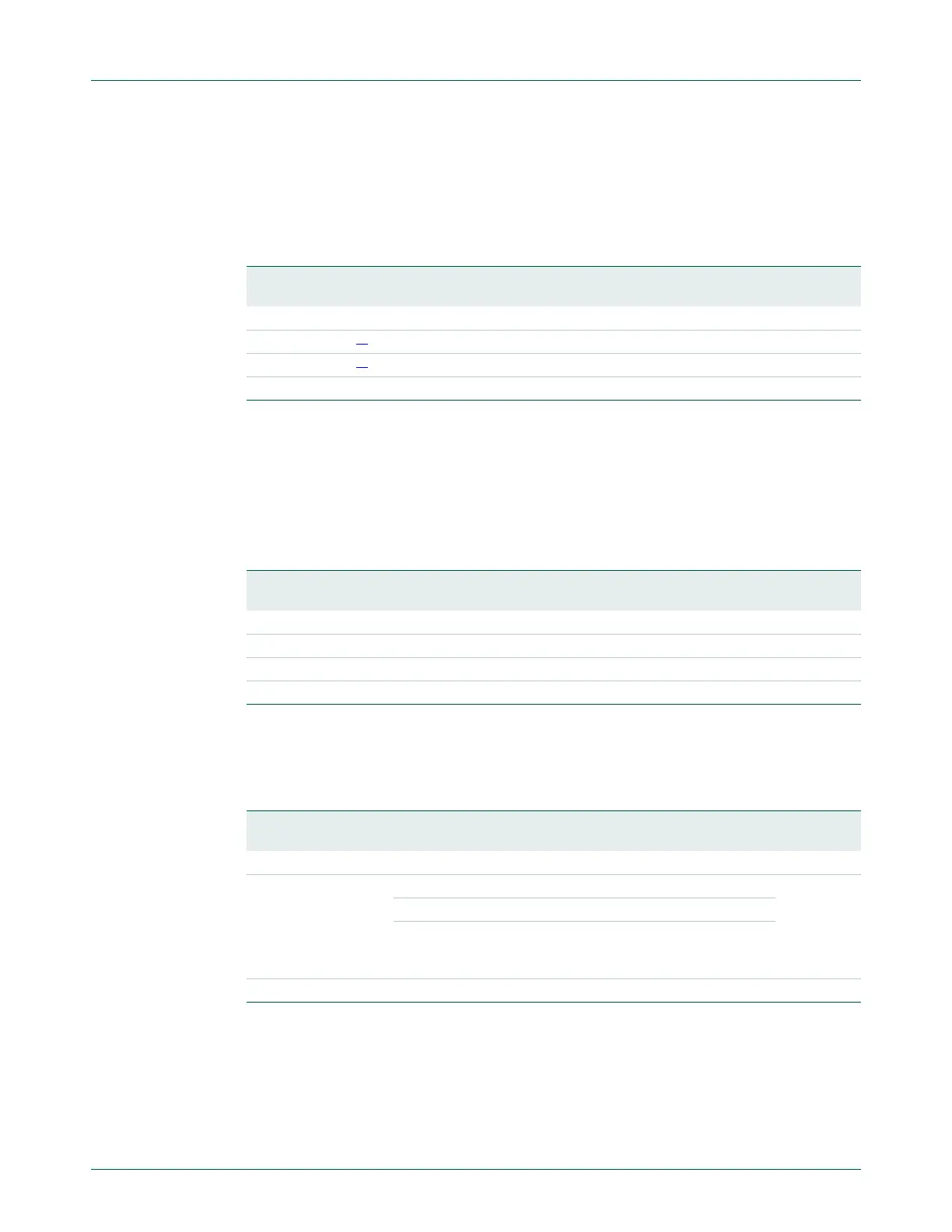

8.5.7 Pin Function Select Register 9 (PINSEL9 - 0x4002 C024)

The PINSEL9 register controls the functions of the upper half of Port 4. The direction

control bit in the FIO4DIR register is effective only when the GPIO function is selected for

a pin. For other functions, direction is controlled automatically.

8.5.8 Pin Function Select Register 10 (PINSEL10 - 0x4002 C028)

Only bit 3 of this register is used to control the Trace function on pins P2.2 through P2.6.

Table 84. Pin function select register 7 (PINSEL7 - address 0x4002 C01C) bit description

PINSEL7 Pin

name

Function when

00

Function

when 01

Function

when 10

Function

when 11

Reset

value

17:0 - Reserved Reserved Reserved Reserved 0

19:18 P3.25

[1]

GPIO Port 3.25 Reserved MAT0.0 PWM1.2 00

21:20 P3.26

[1]

GPIO Port 3.26 STCLK MAT0.1 PWM1.3 00

31:22 - Reserved Reserved Reserved Reserved 0

Table 85. Pin function select register 9 (PINSEL9 - address 0x4002 C024) bit description

PINSEL9 Pin

name

Function when

00

Function

when 01

Function

when 10

Function

when 11

Reset

value

23:0 - Reserved Reserved Reserved Reserved 00

25:24 P4.28 GPIO Port 4.28 RX_MCLK MAT2.0 TXD3 00

27:26 P4.29 GPIO Port 4.29 TX_MCLK MAT2.1 RXD3 00

31:28 - Reserved Reserved Reserved Reserved 00

Table 86. Pin function select register 10 (PINSEL10 - address 0x4002 C028) bit description

Bit Symbol Value Description Reset

value

2:0 - - Reserved. Software should not write 1 to these bits. NA

3 GPIO/TRACE TPIU interface pins control. 0

0 TPIU interface is disabled.

1 TPIU interface is enabled. TPIU signals are

available on the pins hosting them regardless of the

PINSEL4 content.

31:4 - - Reserved. Software should not write 1 to these bits. NA

Loading...

Loading...