UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 407 of 841

NXP Semiconductors

UM10360

Chapter 17: LPC176x/5x SPI

Register has been read when the SPIF status is active. If the SPI Data Register is written

in this time frame, the write data will be lost, and the write collision (WCOL) bit in the SPI

Status Register will be activated.

Mode Fault

If the SSEL signal goes active when the SPI block is a master, this indicates another

master has selected the device to be a slave. This condition is known as a mode fault.

When a mode fault is detected, the mode fault (MODF) bit in the SPI Status Register will

be activated, the SPI signal drivers will be de-activated, and the SPI mode will be changed

to be a slave.

If the SSEL function is assigned to its related pin in the relevant Pin Function Select

Register, the SSEL signal must always be inactive when the SPI controller is a master.

Slave Abort

A slave transfer is considered to be aborted if the SSEL signal goes inactive before the

transfer is complete. In the event of a slave abort, the transmit and receive data for the

transfer that was in progress are lost, and the slave abort (ABRT) bit in the SPI Status

Register will be activated.

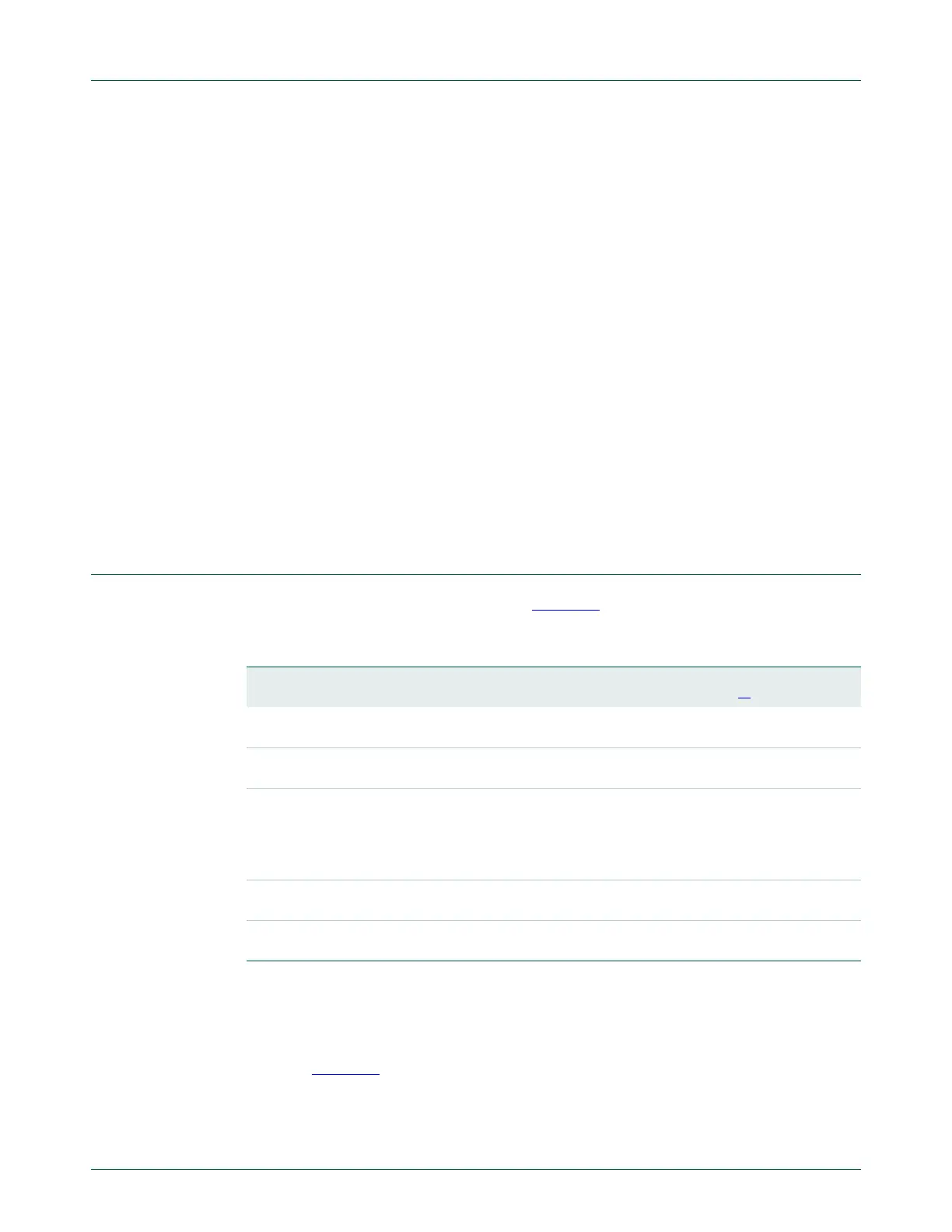

17.7 Register description

The SPI contains 5 registers as shown in Table 360. All registers are byte, half word and

word accessible.

[1] Reset Value reflects the data stored in used bits only. It does not include reserved bits content.

17.7.1 SPI Control Register (S0SPCR - 0x4002 0000)

The S0SPCR register controls the operation of SPI0 as per the configuration bits setting

shown in Table 361

.

Table 360. SPI register map

Name Description Access Reset

Value

[1]

Address

S0SPCR SPI Control Register. This register controls the

operation of the SPI.

R/W 0x00 0x4002 0000

S0SPSR SPI Status Register. This register shows the

status of the SPI.

RO 0x00 0x4002 0004

S0SPDR SPI Data Register. This bi-directional register

provides the transmit and receive data for the

SPI. Transmit data is provided to the SPI0 by

writing to this register. Data received by the SPI0

can be read from this register.

R/W 0x00 0x4002 0008

S0SPCCR SPI Clock Counter Register. This register

controls the frequency of a master’s SCK0.

R/W 0x00 0x4002 000C

S0SPINT SPI Interrupt Flag. This register contains the

interrupt flag for the SPI interface.

R/W 0x00 0x4002 001C

Loading...

Loading...