UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 272 of 841

NXP Semiconductors

UM10360

Chapter 12: LPC176x/5x USB Host controller

12.4.1 Pin description

12.4.1.1 USB host usage note

The USB block can be configured as USB host. For details on how to connect the USB

port, see the USB OTG chapter, Section 13.7

.

The USB device/host/OTG controller is disabled after RESET and must be enabled by

writing a 1 to the PCUSB bit in the PCONP register, see Table 46

.

12.4.2 Software interface

The software interface of the USB host block consists of a register view and the format

definitions for the endpoint descriptors. For details on these two aspects see the OHCI

specification. The register map is shown in the next subsection.

12.4.2.1 Register map

The following registers are located in the AHB clock ‘cclk’ domain. They can be accessed

directly by the processor. All registers are 32 bits wide and aligned in the word address

boundaries.

Table 253. USB Host port pins

Pin name Direction Description Type

USB_D+ I/O Positive differential data USB Connector

USB_D

I/O Negative differential data USB Connector

USB_UP_LED O GoodLink LED control signal Control

U

SB_PPWR O Port power enable Host power switch

USB_PWRD I Port power status Host power switch

U

SB_OVRCR I Over-current status Host power switch

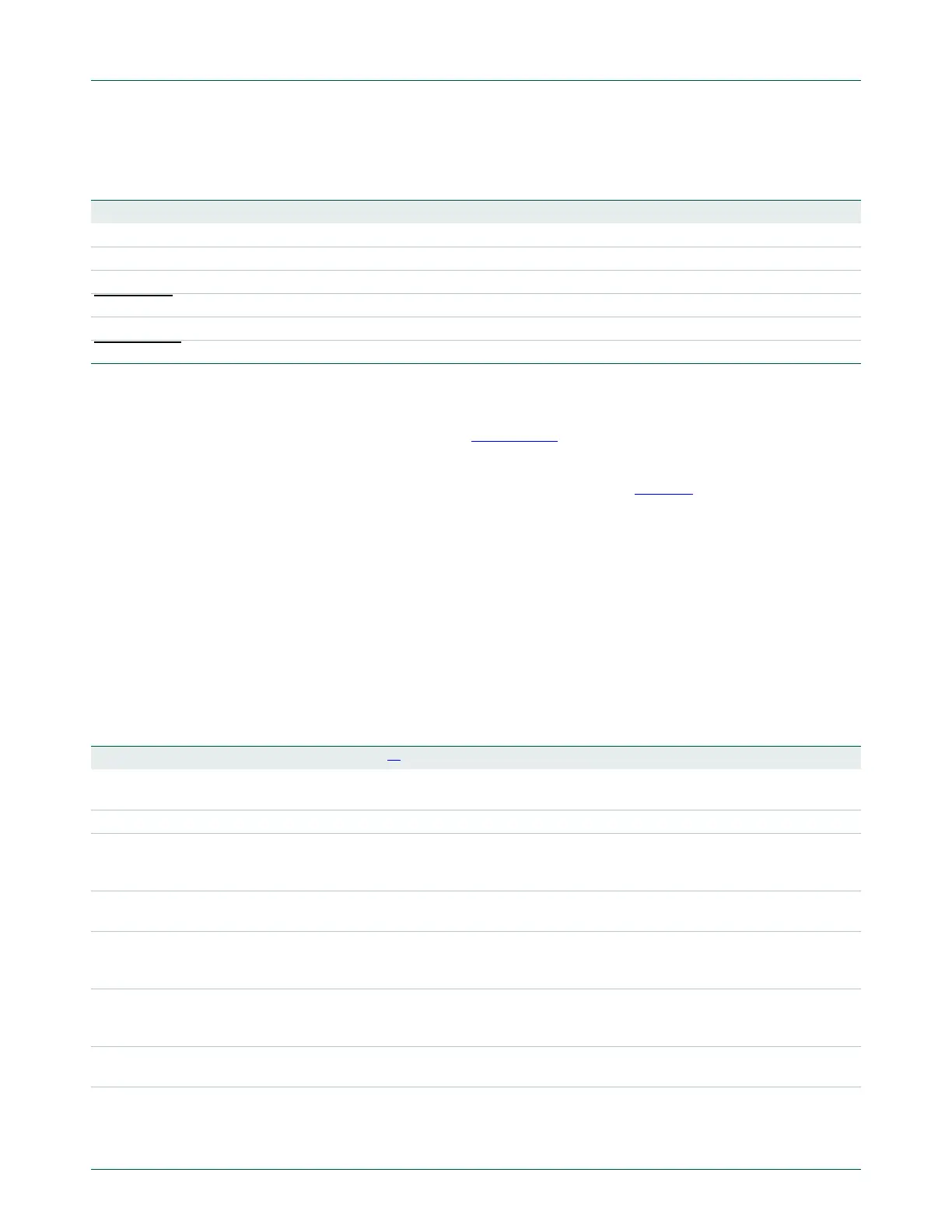

Table 254. USB Host register address definitions

Name Address R/W

[1]

Function Reset value

HcRevision 0x5000 C000 R BCD representation of the version of the HCI

specification that is implemented by the Host Controller.

0x10

HcControl 0x5000 C004 R/W Defines the operating modes of the HC. 0x0

HcCommandStatus 0x5000 C008 R/W This register is used to receive the commands from the

Host Controller Driver (HCD). It also indicates the status

of the HC.

0x0

HcInterruptStatus 0x5000 C00C R/W Indicates the status on various events that cause

hardware interrupts by setting the appropriate bits.

0x0

HcInterruptEnable 0x5000 C010 R/W Controls the bits in the HcInterruptStatus register and

indicates which events will generate a hardware

interrupt.

0x0

HcInterruptDisable 0x5000 C014 R/W The bits in this register are used to disable

corresponding bits in the HCInterruptStatus register and

in turn disable that event leading to hardware interrupt.

0x0

HcHCCA 0x5000 C018 R/W Contains the physical address of the host controller

communication area.

0x0

HcPeriodCurrentED 0x5000 C01C R Contains the physical address of the current isochronous

or interrupt endpoint descriptor.

0x0

Loading...

Loading...