UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 20 December 2013 769 of 841

NXP Semiconductors

UM10360

Chapter 34: Appendix: Cortex-M3 user guide

34.4.3.2.1 About IT folding

In some situations, the processor can start executing the first instruction in an IT block

while it is still executing the

IT

instruction. This behavior is called IT folding, and improves

performance, However, IT folding can cause jitter in looping. If a task must avoid jitter, set

the DISFOLD bit to 1 before executing the task, to disable IT folding.

34.4.3.3 CPUID Base Register

The CPUID register contains the processor part number, version, and implementation

information. See the register summary in Table 654

for its attributes. The bit assignments

are shown in Table 656

.

34.4.3.4 Interrupt Control and State Register

The ICSR:

• provides:

– a set-pending bit for the Non-Maskable Interrupt (NMI) exception

– set-pending and clear-pending bits for the PendSV and SysTick exceptions

• indicates:

– the exception number of the exception being processed

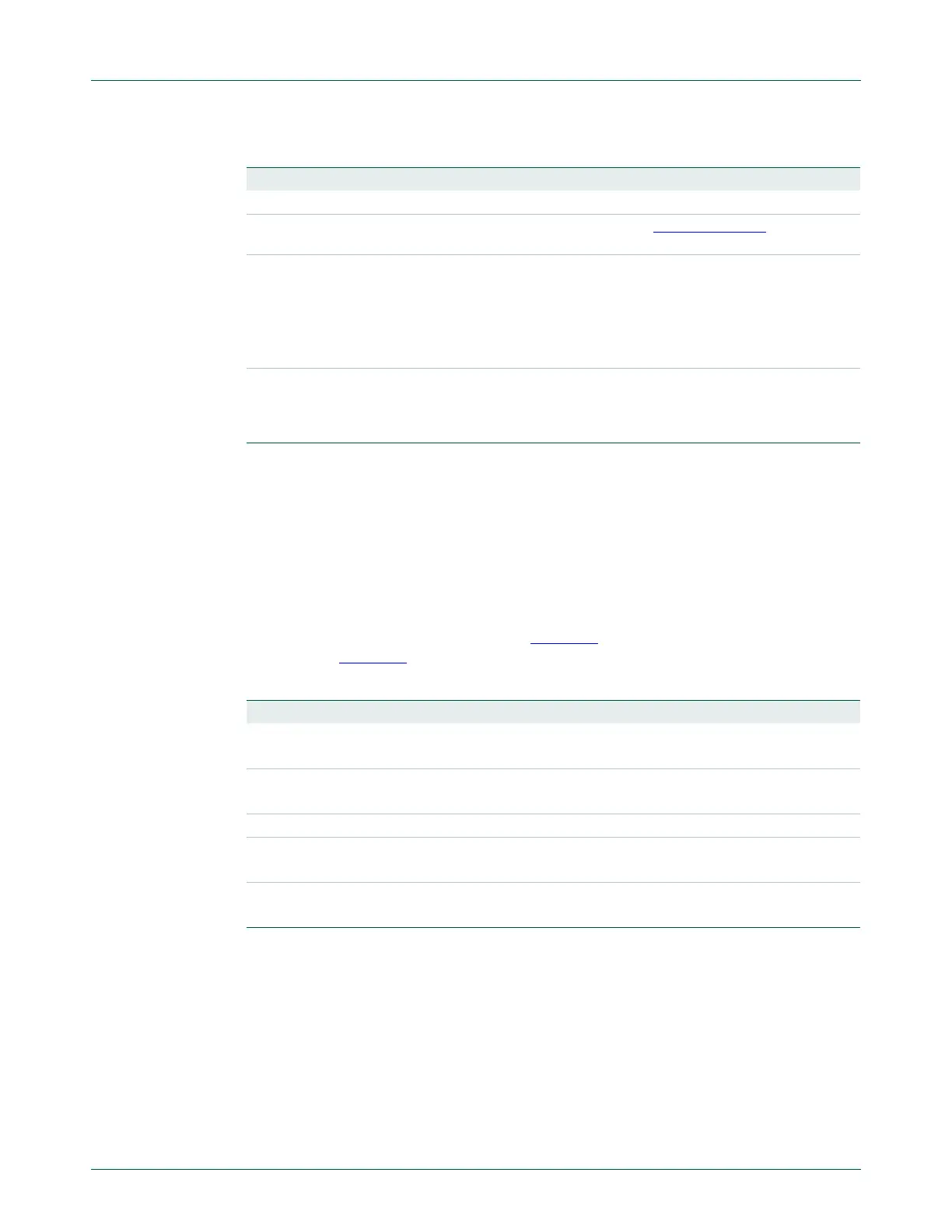

Table 655. ACTLR bit assignments

Bits Name Function

[31:3] - Reserved

[2] DISFOLD When set to 1, disables IT folding. see Section 34.4.3.2.1

for more

information.

[1] DISDEFWBUF When set to 1, disables write buffer use during default memory map

accesses. This causes all bus faults to be precise bus faults but

decreases performance because any store to memory must complete

before the processor can execute the next instruction.

Remark: This bit only affects write buffers implemented in the

Cortex-M3 processor.

[0] DISMCYCINT When set to 1, disables interruption of load multiple and store multiple

instructions. This increases the interrupt latency of the processor

because any LDM or STM must complete before the processor can

stack the current state and enter the interrupt handler.

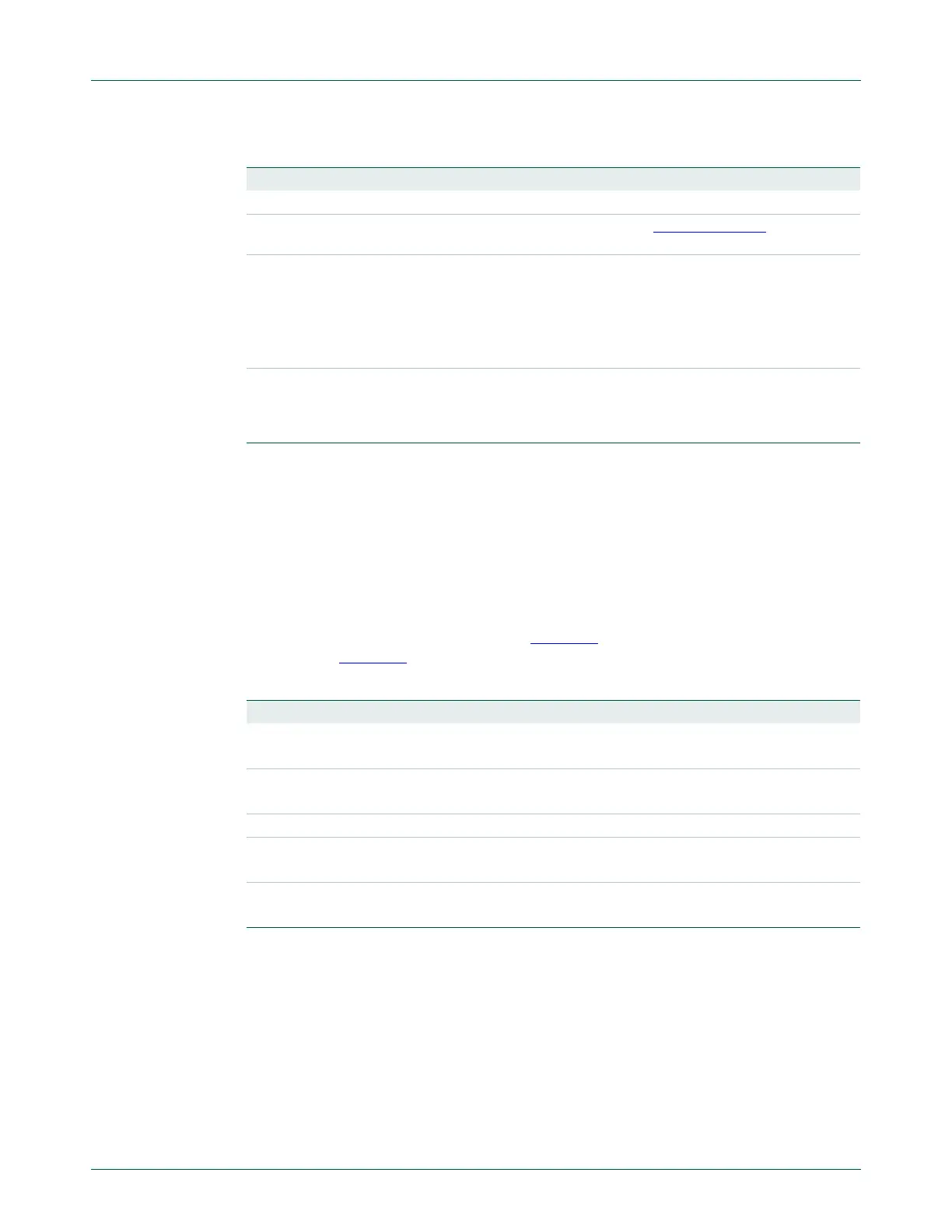

Table 656. CPUID register bit assignments

Bits Name Function

[31:24] Implementer Implementer code:

0x41

= ARM

[23:20] Variant Variant number, the r value in the r

npn product revision identifier:

0x2 = r2p0

[19:16] Constant Reads as

0xF

[15:4] PartNo Part number of the processor:

0xC23

= Cortex-M3

[3:0] Revision Revision number, the p value in the r

npn product revision identifier:

0x0 = r2p0

Loading...

Loading...