UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 132 of 841

NXP Semiconductors

UM10360

Chapter 9: LPC176x/5x General Purpose Input/Output (GPIO)

9.5.6 GPIO interrupt registers

The following registers configure the pins of Port 0 and Port 2 to generate interrupts.

9.5.6.1 GPIO overall Interrupt Status register (IOIntStatus - 0x4002 8080)

This read-only register indicates the presence of interrupt pending on all of the GPIO ports

that support GPIO interrupts. Only status one bit per port is required.

9.5.6.2 GPIO Interrupt Enable for port 0 Rising Edge (IO0IntEnR - 0x4002 8090)

Each bit in these read-write registers enables the rising edge interrupt for the

corresponding port 0 pin.

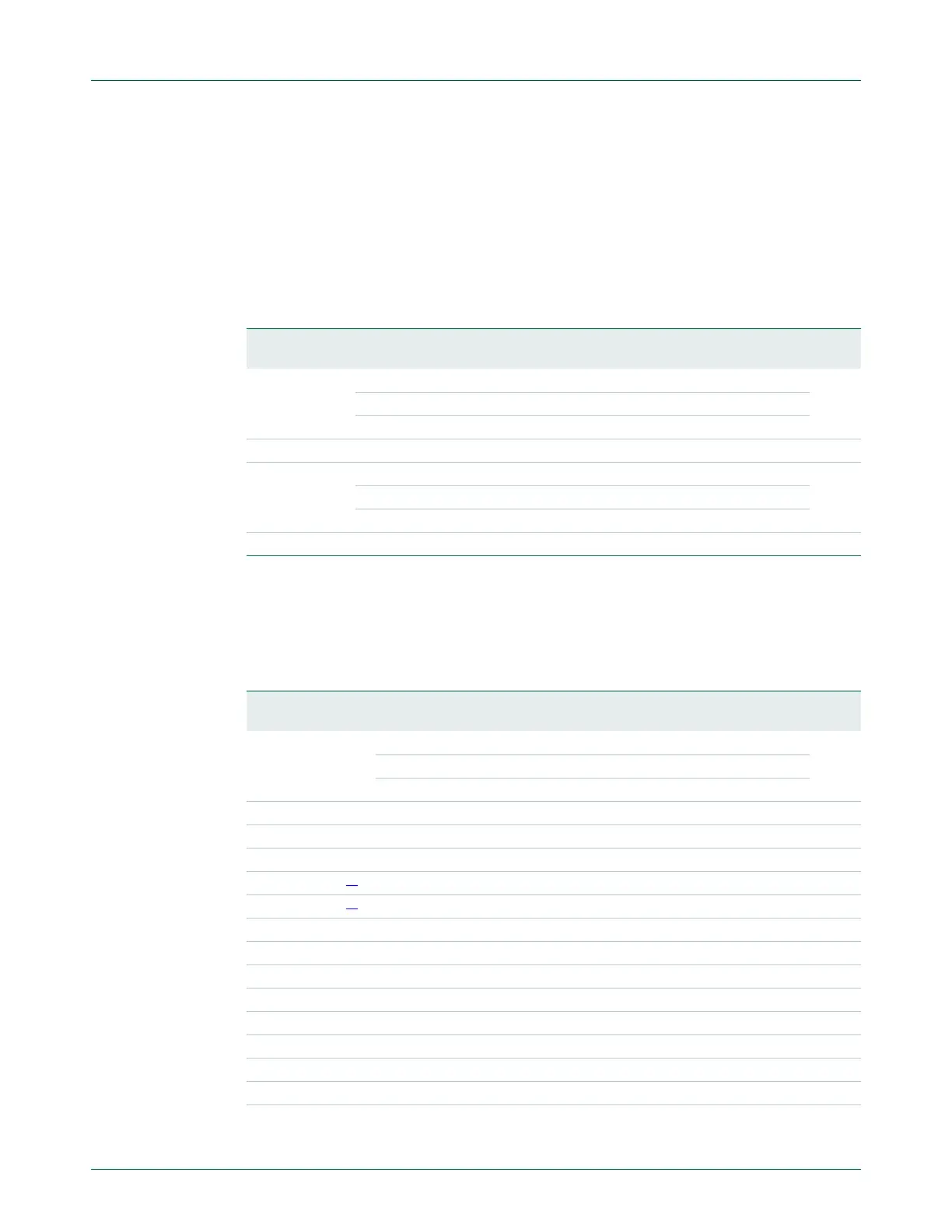

Table 113. GPIO overall Interrupt Status register (IOIntStatus - address 0x4002 8080) bit

description

Bit Symbol Value Description Reset

value

0 P0Int Port 0 GPIO interrupt pending. 0

0 There are no pending interrupts on Port 0.

1 There is at least one pending interrupt on Port 0.

1 - - Reserved. The value read from a reserved bit is not defined. NA

2 P2Int Port 2 GPIO interrupt pending. 0

0 There are no pending interrupts on Port 2.

1 There is at least one pending interrupt on Port 2.

31:2 - - Reserved. The value read from a reserved bit is not defined. NA

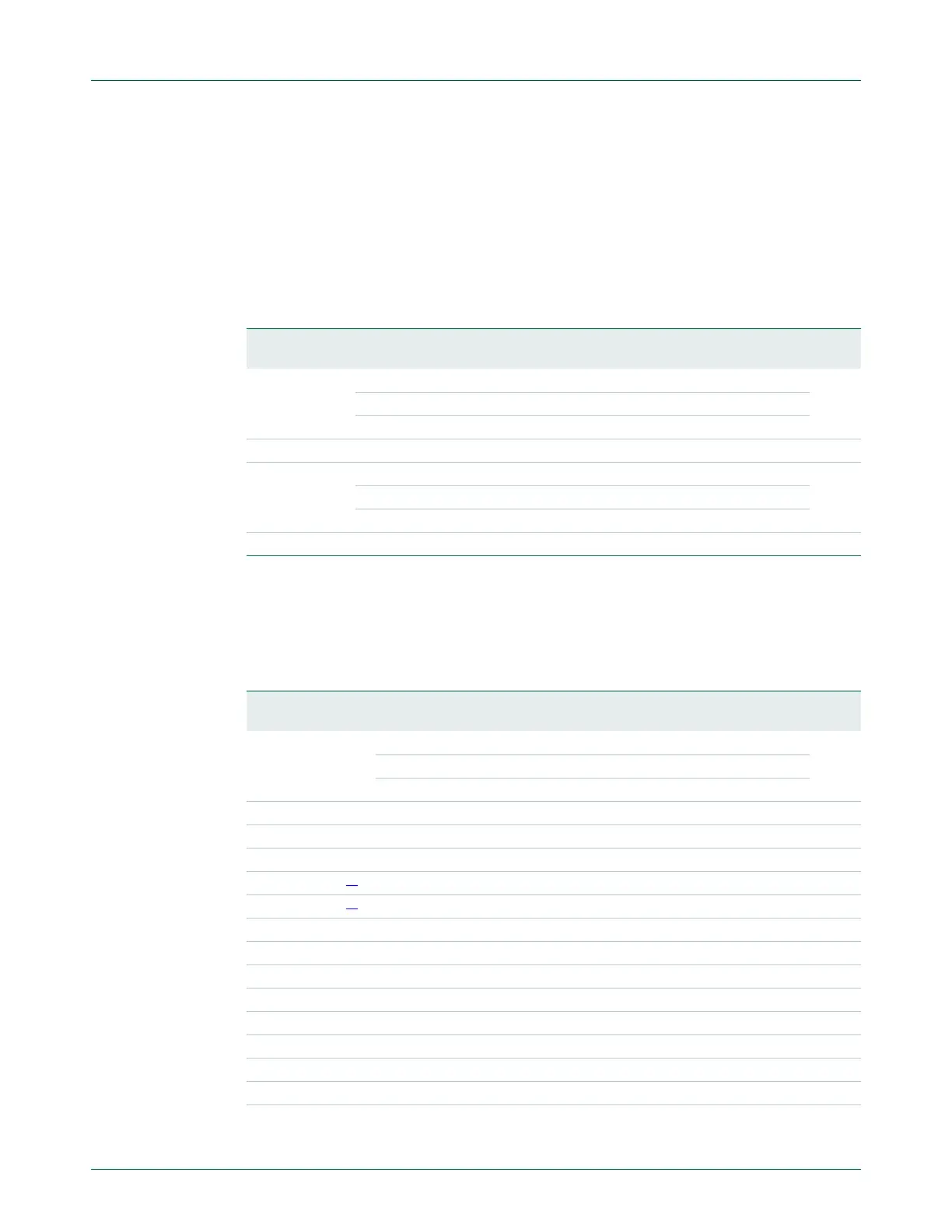

Table 114. GPIO Interrupt Enable for port 0 Rising Edge (IO0IntEnR - 0x4002 8090) bit

description

Bit Symbol Value Description Reset

value

0 P0.0ER Enable rising edge interrupt for P0.0. 0

0 Rising edge interrupt is disabled on P0.0.

1 Rising edge interrupt is enabled on P0.0.

1 P0.1ER Enable rising edge interrupt for P0.1. 0

2 P0.2ER Enable rising edge interrupt for P0.2. 0

3 P0.3ER Enable rising edge interrupt for P0.3. 0

4 P0.4ER

[1]

Enable rising edge interrupt for P0.4. 0

5 P0.5ER

[1]

Enable rising edge interrupt for P0.5. 0

6 P0.6ER Enable rising edge interrupt for P0.6. 0

7 P0.7ER Enable rising edge interrupt for P0.7. 0

8 P0.8ER Enable rising edge interrupt for P0.8. 0

9 P0.9ER Enable rising edge interrupt for P0.9. 0

10 P0.10ER Enable rising edge interrupt for P0.10. 0

11 P0.11ER Enable rising edge interrupt for P0.11. 0

14:12 - Reserved NA

15 P0.15ER Enable rising edge interrupt for P0.15. 0

16 P0.16ER Enable rising edge interrupt for P0.16. 0

Loading...

Loading...