UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 526 of 841

NXP Semiconductors

UM10360

Chapter 25: LPC176x/5x Motor control PWM

25.7 Register description

“Control” registers and “interrupt” registers have separate read, set, and clear addresses.

Reading such a register’s read address(e.g. MCCON) yields the state of the register bits.

Writing ones to the set address (e.g. MCCON_SET) sets register bit(s), and writing ones

to the clear address (e.g. MCCON_CLR) clears register bit(s).

The Capture registers (MCCAP) are read-only, and the write-only MCCAP_CLR address

can be used to clear one or more of them. All the other MCPWM registers (MCTIM,

MCPER, MCPW, MCDEADTIME, and MCCP) are normal read-write registers.

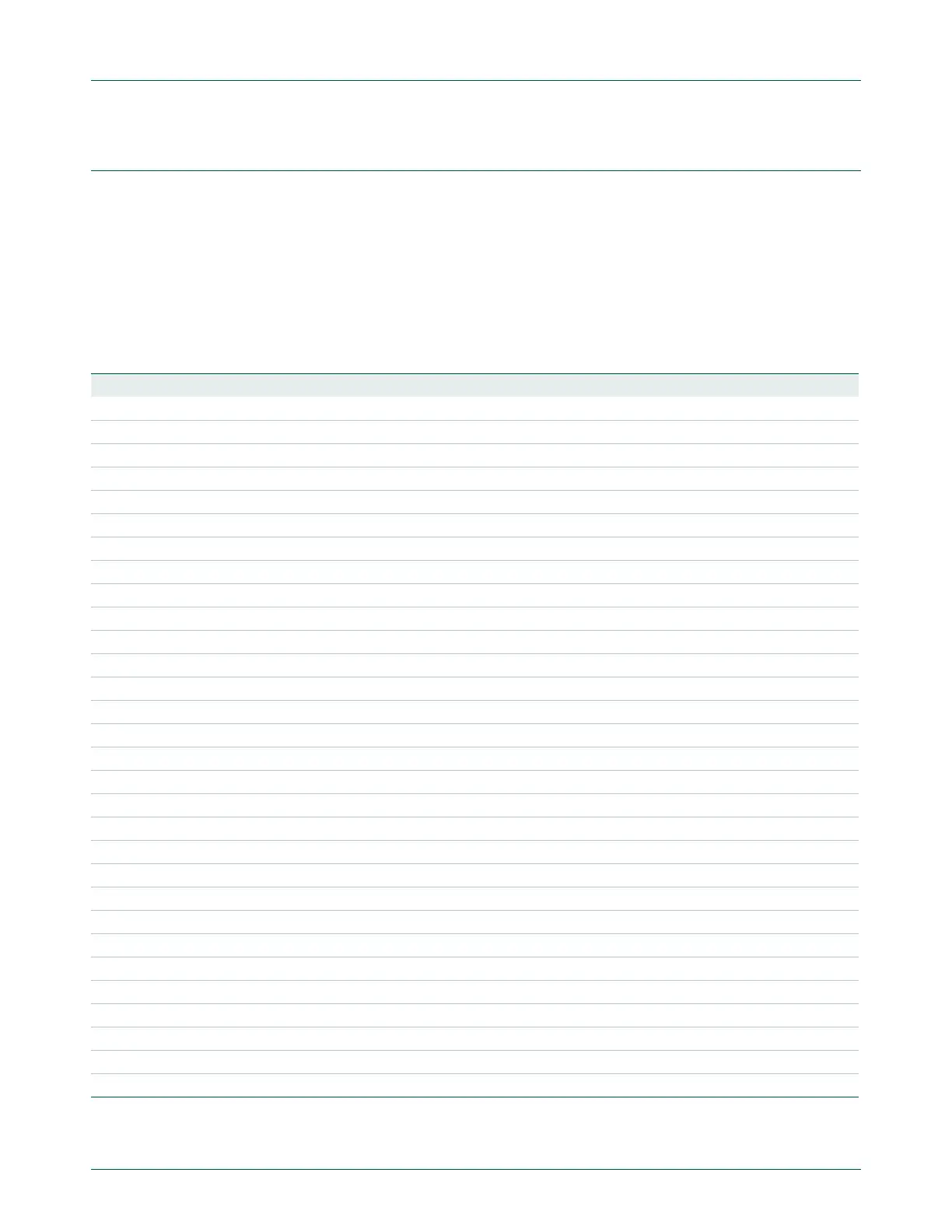

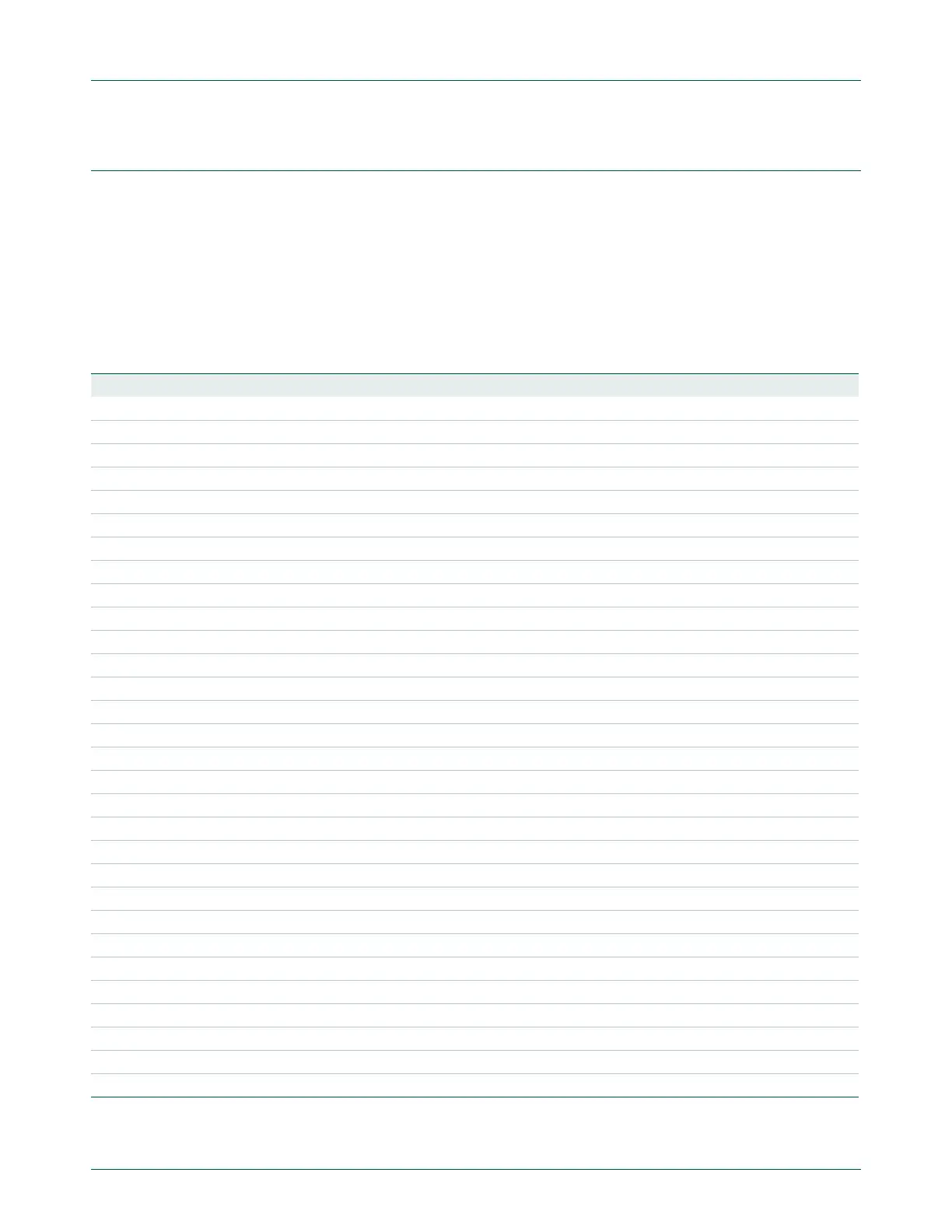

Table 454. Motor Control Pulse Width Modulator (MCPWM) register map

Name Description Access Reset value Address

MCCON PWM Control read address RO 0 0x400B 8000

MCCON_SET PWM Control set address WO - 0x400B 8004

MCCON_CLR PWM Control clear address WO - 0x400B 8008

MCCAPCON Capture Control read address RO 0 0x400B 800C

MCCAPCON_SET Capture Control set address WO - 0x400B 8010

MCCAPCON_CLR Event Control clear address WO - 0x400B 8014

MCTC0 Timer Counter register, channel 0 R/W 0 0x400B 8018

MCTC1 Timer Counter register, channel 1 R/W 0 0x400B 801C

MCTC2 Timer Counter register, channel 2 R/W 0 0x400B 8020

MCLIM0 Limit register, channel 0 R/W 0xFFFF FFFF 0x400B 8024

MCLIM1 Limit register, channel 1 R/W 0xFFFF FFFF 0x400B 8028

MCLIM2 Limit register, channel 2 R/W 0xFFFF FFFF 0x400B 802C

MCMAT0 Match register, channel 0 R/W 0xFFFF FFFF 0x400B 8030

MCMAT1 Match register, channel 1 R/W 0xFFFF FFFF 0x400B 8034

MCMAT2 Match register, channel 2 R/W 0xFFFF FFFF 0x400B 8038

MCDT Dead time register R/W 0x3FFF FFFF 0x400B 803C

MCCP Commutation Pattern register R/W 0 0x400B 8040

MCCAP0 Capture register, channel 0 RO 0 0x400B 8044

MCCAP1 Capture register, channel 1 RO 0 0x400B 8048

MCCAP2 Capture register, channel 2 RO 0 0x400B 804C

MCINTEN Interrupt Enable read address RO 0 0x400B 8050

MCINTEN_SET Interrupt Enable set address WO - 0x400B 8054

MCINTEN_CLR Interrupt Enable clear address WO - 0x400B 8058

MCCNTCON Count Control read address RO 0 0x400B 805C

MCCNTCON_SET Count Control set address WO - 0x400B 8060

MCCNTCON_CLR Count Control clear address WO - 0x400B 8064

MCINTF Interrupt flags read address RO 0 0x400B 8068

MCINTF_SET Interrupt flags set address WO - 0x400B 806C

MCINTF_CLR Interrupt flags clear address WO - 0x400B 8070

MCCAP_CLR Capture clear address WO - 0x400B 8074

Loading...

Loading...