UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 572 of 841

NXP Semiconductors

UM10360

Chapter 28: LPC176x/5x Watchdog Timer (WDT)

28.4.1 Watchdog Mode register (WDMOD - 0x4000 0000)

The WDMOD register controls the operation of the Watchdog as per the combination of

WDEN and RESET bits. Note that a watchdog feed must be performed before any

changes to the WDMOD register take effect.

Once the WDEN and/or WDRESET bits are set they can not be cleared by software. Both

flags are cleared by an external reset or a Watchdog timer underflow.

WDTOF The Watchdog time-out flag is set when the Watchdog times out. This flag is

cleared by software.

WDINT The Watchdog interrupt flag is set when the Watchdog times out. This flag is

cleared when any reset occurs. Once the watchdog interrupt is serviced, it can be

disabled in the NVIC or the watchdog interrupt request will be generated indefinitely. the

intent of the watchdog interrupt is to allow debugging watchdog activity without resetting

the device when the watchdog overflows.

Watchdog reset or interrupt will occur any time the watchdog is running and has an

operating clock source. Any clock source works in Sleep mode, and the IRC works in

Deep Sleep mode. If a watchdog interrupt occurs in Sleep or Deep Sleep mode, it will

wake up the device.

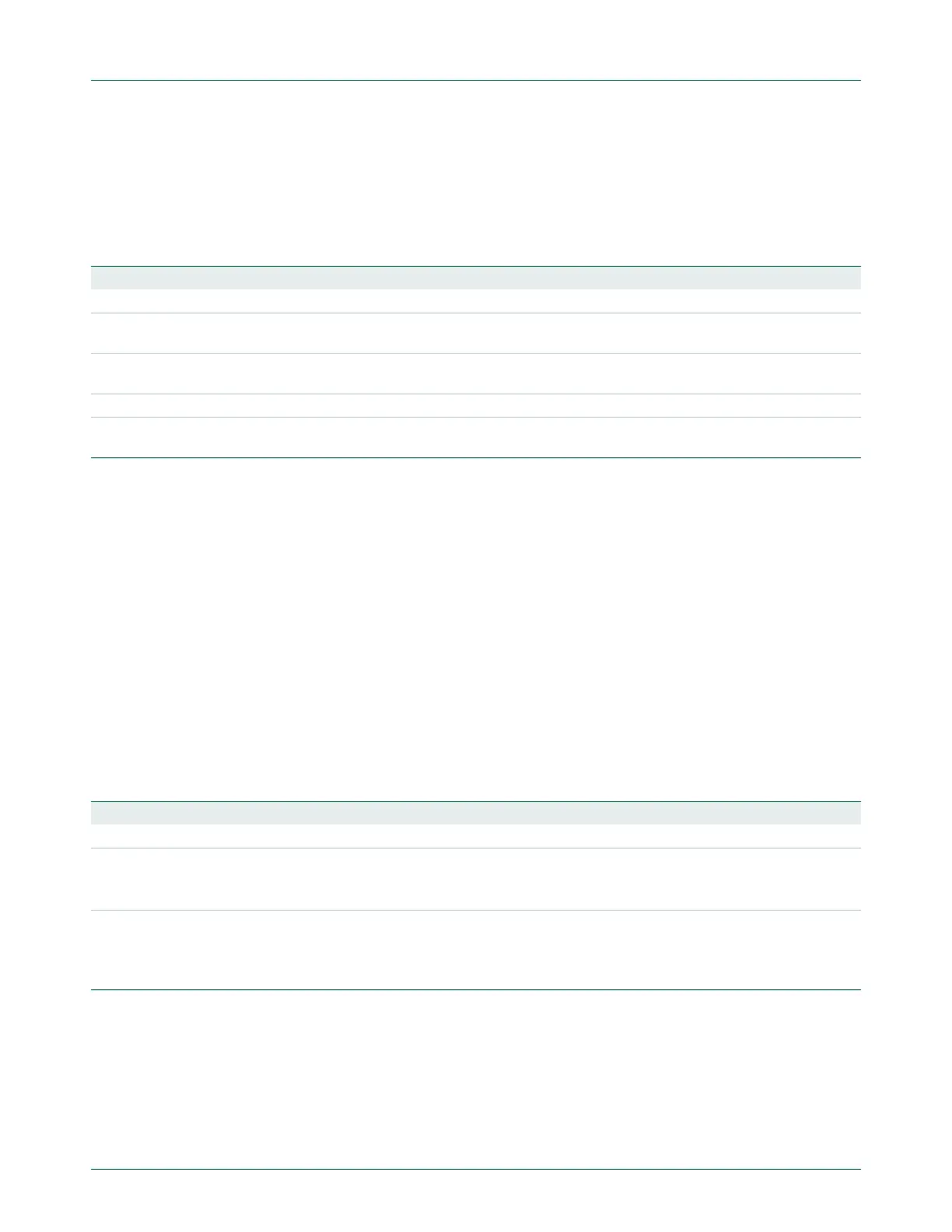

Table 523: Watchdog Mode register (WDMOD, address 0x4000 0000) bit description

Bit Symbol Description Reset Value

0 WDEN WDEN Watchdog enable bit (set-only). When 1, the watchdog timer is running. 0

1 WDRESET WDRESET Watchdog reset enable bit (set -only). When 1, a watchdog time-out will

cause a chip reset.

0

2 WDTOF WDTOF Watchdog time-out flag. Set when the watchdog timer times out, cleared by

software.

0 (Only after

external reset)

3 WDINT WDINT Watchdog interrupt flag (read-only, not clearable by software). 0

31:4 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

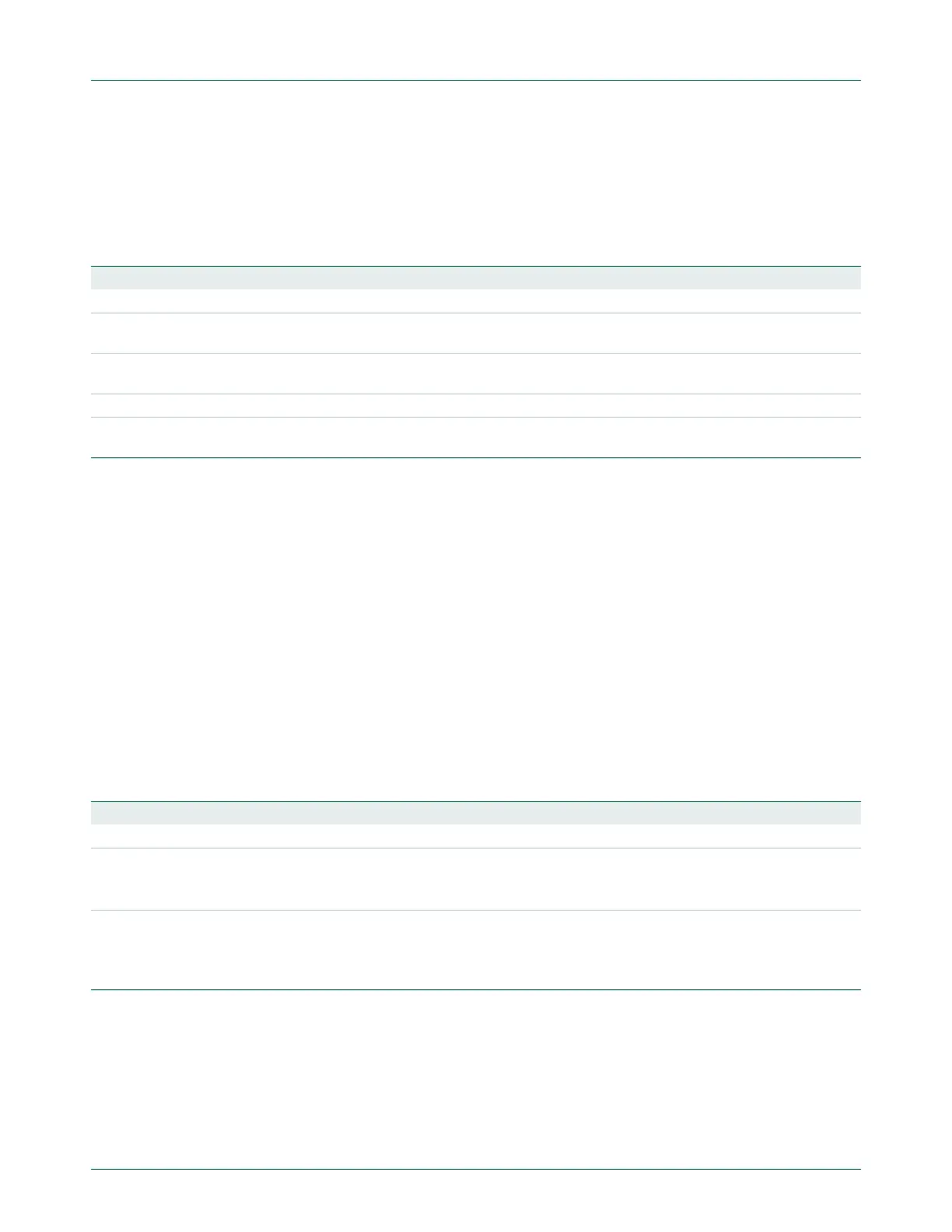

Table 524. Watchdog operating modes selection

WDEN WDRESET Mode of Operation

0 X (0 or 1) Debug/Operate without the Watchdog running.

1 0 Watchdog interrupt mode: debug with the Watchdog interrupt but no WDRESET enabled.

When this mode is selected, a watchdog counter underflow will set the WDINT flag and the

Watchdog interrupt request will be generated.

1 1 Watchdog reset mode: operate with the Watchdog interrupt and WDRESET enabled.

When this mode is selected, a watchdog counter underflow will reset the microcontroller. Although

the Watchdog interrupt is also enabled in this case (WDEN = 1) it will not be recognized since the

watchdog reset will clear the WDINT flag.

Loading...

Loading...