UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 578 of 841

NXP Semiconductors

UM10360

Chapter 29: LPC176x/5x Analog-to-Digital Converter (ADC)

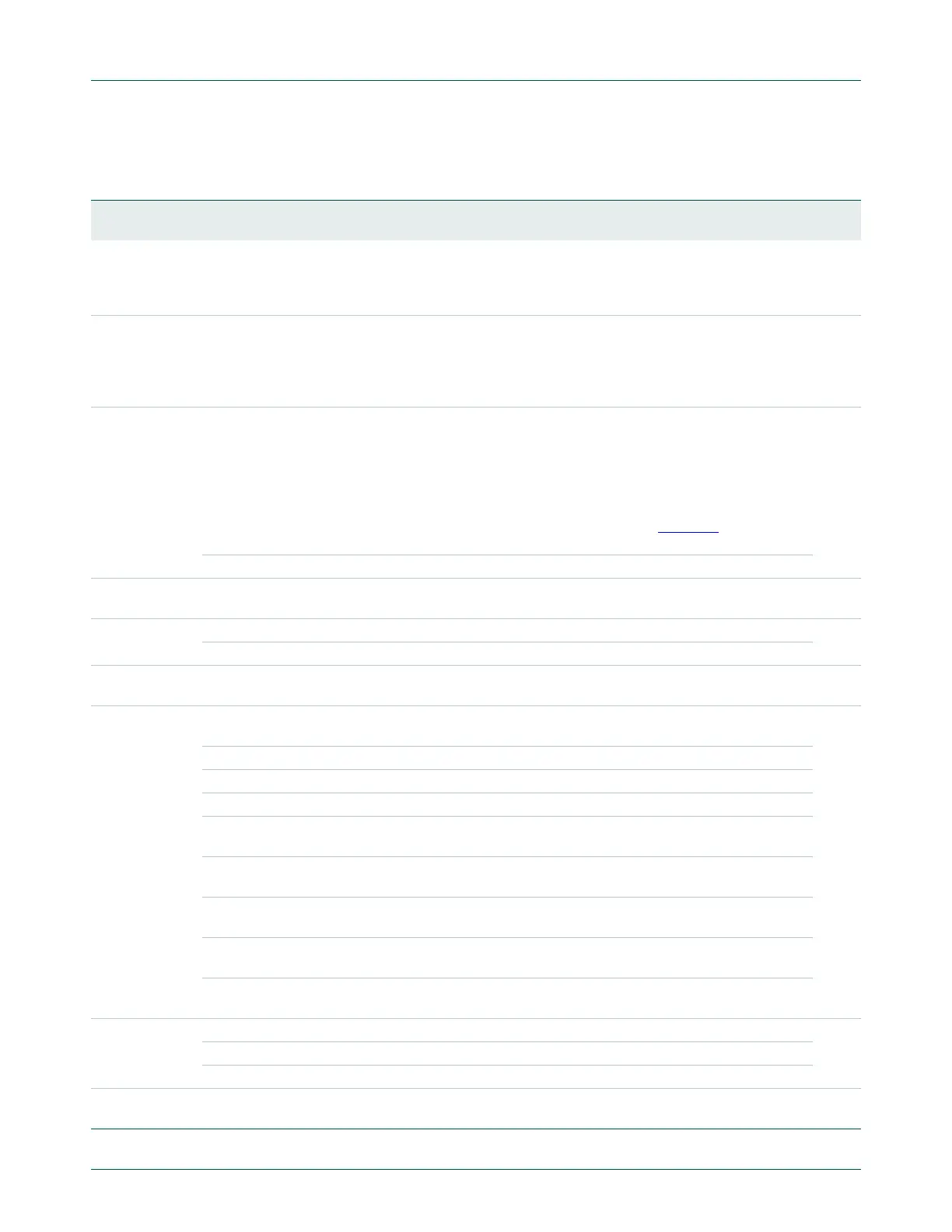

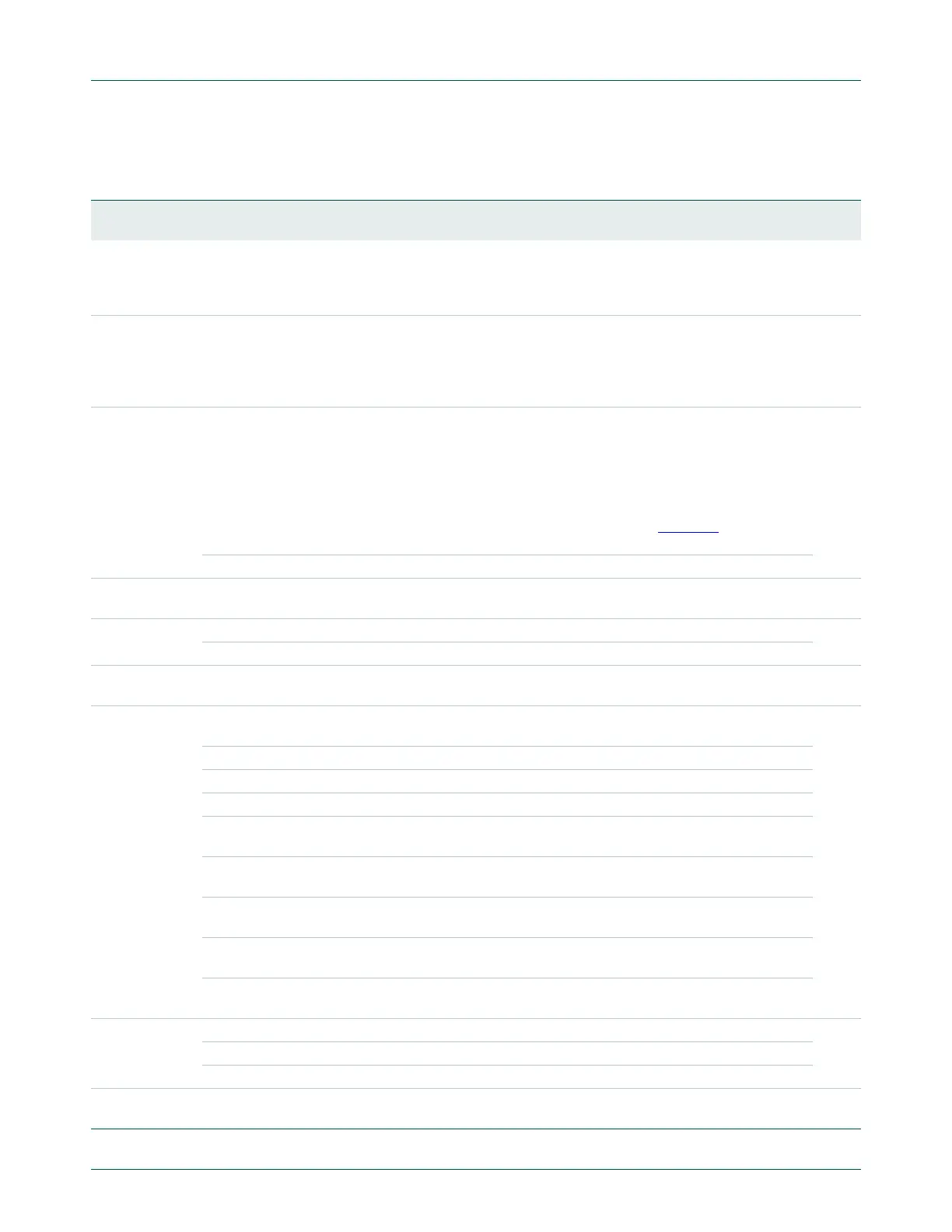

29.5.1 A/D Control Register (AD0CR - 0x4003 4000)

Table 531: A/D Control Register (AD0CR - address 0x4003 4000) bit description

Bit Symbol Value Description Reset

value

7:0 SEL Selects which of the AD0.7:0 pins is (are) to be sampled and converted. For AD0, bit 0

selects Pin AD0.0, and bit 7 selects pin AD0.7. In software-controlled mode, only one of

these bits should be 1. In hardware scan mode, any value containing 1 to 8 ones is

allowed. All zeroes is equivalent to 0x01.

0x01

15:8 CLKDIV The APB clock (PCLK_ADC0) is divided by (this value plus one) to produce the clock for

the A/D converter, which should be less than or equal to 13 MHz. Typically, software

should program the smallest value in this field that yields a clock of 13 MHz or slightly

less, but in certain cases (such as a high-impedance analog source) a slower clock may

be desirable.

0

16 BURST 1 The AD converter does repeated conversions at up to 200 kHz, scanning (if necessary)

through the pins selected by bits set to ones in the SEL field. The first conversion after the

start corresponds to the least-significant 1 in the SEL field, then higher numbered 1-bits

(pins) if applicable. Repeated conversions can be terminated by clearing this bit, but the

conversion that’s in progress when this bit is cleared will be completed.

Remark: START bits must be 000 when BURST = 1 or conversions will not start. If

BURST is set to 1, the ADGINTEN bit in the AD0INTEN register (Table 533

) must be set

to 0.

0

0 Conversions are software controlled and require 65 clocks.

20:17 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

21 PDN 1 The A/D converter is operational. 0

0 The A/D converter is in power-down mode.

23:22 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

26:24 START When the BURST bit is 0, these bits control whether and when an A/D conversion is

started:

0

000 No start (this value should be used when clearing PDN to 0).

001 Start conversion now.

010 Start conversion when the edge selected by bit 27 occurs on the P2.10 / EINT0 / NMI pin.

011 Start conversion when the edge selected by bit 27 occurs on the P1.27 / CLKOUT /

USB_OVRCRn / CAP0.1 pin.

100 Start conversion when the edge selected by bit 27 occurs on MAT0.1. Note that this does

not require that the MAT0.1 function appear on a device pin.

101 Start conversion when the edge selected by bit 27 occurs on MAT0.3. Note that it is not

possible to cause the MAT0.3 function to appear on a device pin.

110 Start conversion when the edge selected by bit 27 occurs on MAT1.0. Note that this does

not require that the MAT1.0 function appear on a device pin.

111 Start conversion when the edge selected by bit 27 occurs on MAT1.1. Note that this does

not require that the MAT1.1 function appear on a device pin.

27 EDGE This bit is significant only when the START field contains 010-111. In these cases: 0

1 Start conversion on a falling edge on the selected CAP/MAT signal.

0 Start conversion on a rising edge on the selected CAP/MAT signal.

31:28 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

Loading...

Loading...