UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 581 of 841

NXP Semiconductors

UM10360

Chapter 29: LPC176x/5x Analog-to-Digital Converter (ADC)

29.5.5 A/D Status register (ADSTAT - 0x4003 4030)

The A/D Status register allows checking the status of all A/D channels simultaneously.

The DONE and OVERRUN flags appearing in the ADDRn register for each A/D channel

are mirrored in ADSTAT. The interrupt flag (the logical OR of all DONE flags) is also found

in ADSTAT.

29.5.6 A/D Trim register (ADTRIM - 0x4003 4034)

This register will be set by the bootcode on start-up. It contains the trim values for the DAC

and the ADC. The offset trim values for the ADC can be overwritten by the user. All 12 bits

are visible when this register is read.

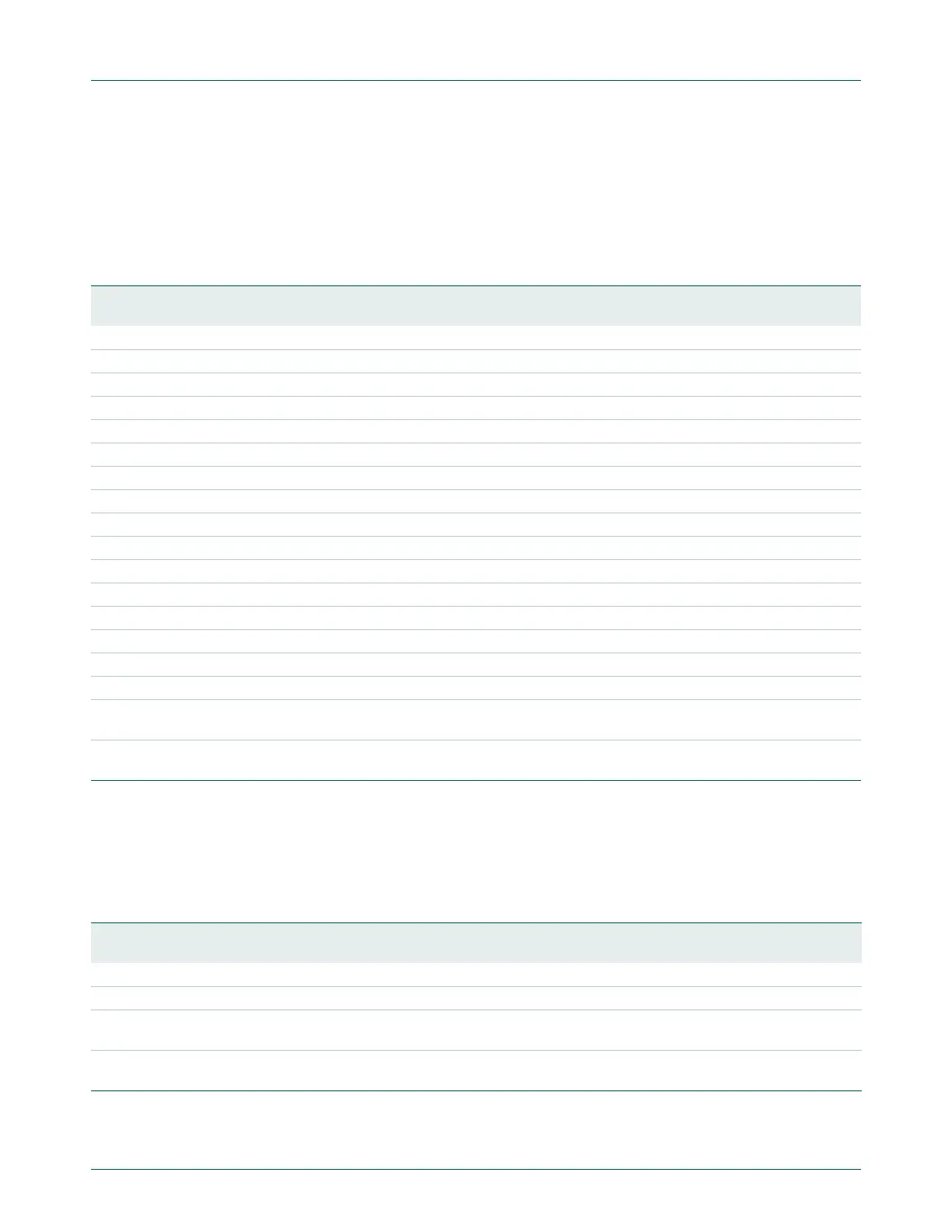

Table 535: A/D Status register (AD0STAT - address 0x4003 4030) bit description

Bit Symbol Description Reset

value

0 DONE0 This bit mirrors the DONE status flag from the result register for A/D channel 0. 0

1 DONE1 This bit mirrors the DONE status flag from the result register for A/D channel 1. 0

2 DONE2 This bit mirrors the DONE status flag from the result register for A/D channel 2. 0

3 DONE3 This bit mirrors the DONE status flag from the result register for A/D channel 3. 0

4 DONE4 This bit mirrors the DONE status flag from the result register for A/D channel 4. 0

5 DONE5 This bit mirrors the DONE status flag from the result register for A/D channel 5. 0

6 DONE6 This bit mirrors the DONE status flag from the result register for A/D channel 6. 0

7 DONE7 This bit mirrors the DONE status flag from the result register for A/D channel 7. 0

8 OVERRUN0 This bit mirrors the OVERRRUN status flag from the result register for A/D channel 0. 0

9 OVERRUN1 This bit mirrors the OVERRRUN status flag from the result register for A/D channel 1. 0

10 OVERRUN2 This bit mirrors the OVERRRUN status flag from the result register for A/D channel 2. 0

11 OVERRUN3 This bit mirrors the OVERRRUN status flag from the result register for A/D channel 3. 0

12 OVERRUN4 This bit mirrors the OVERRRUN status flag from the result register for A/D channel 4. 0

13 OVERRUN5 This bit mirrors the OVERRRUN status flag from the result register for A/D channel 5. 0

14 OVERRUN6 This bit mirrors the OVERRRUN status flag from the result register for A/D channel 6. 0

15 OVERRUN7 This bit mirrors the OVERRRUN status flag from the result register for A/D channel 7. 0

16 ADINT This bit is the A/D interrupt flag. It is one when any of the individual A/D channel Done

flags is asserted and enabled to contribute to the A/D interrupt via the ADINTEN register.

0

31:17 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

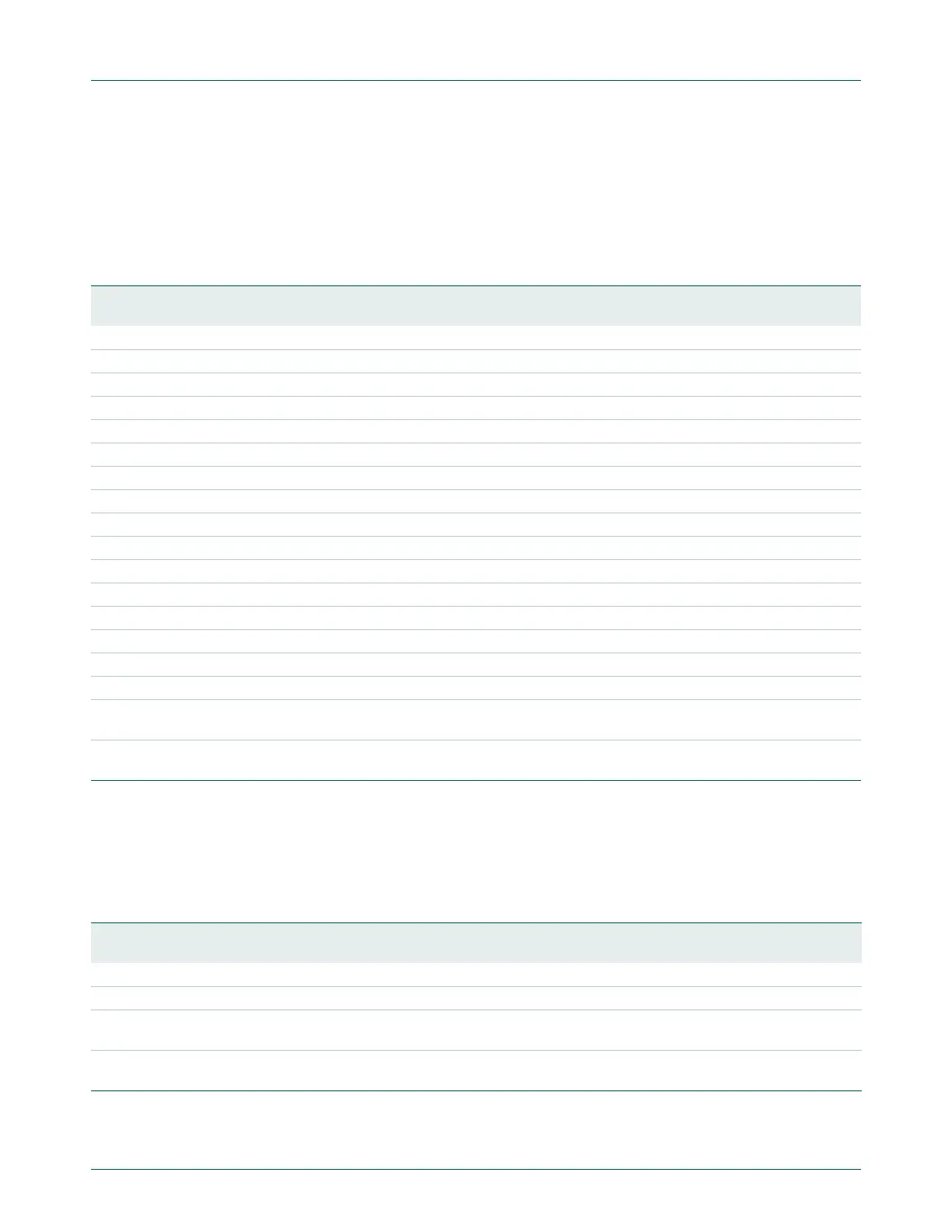

Table 536: A/D Trim register (ADTRM - address 0x4003 4034) bit description

Bit Symbol Description Reset

value

3:0 - reserved. NA

7:4 ADCOFFS Offset trim bits for ADC operation. Initialized by the boot code. Can be overwritten by the user. 0

11:8 TRIM written-to by boot code. Can not be overwritten by the user. These bits are locked after boot

code write.

1111

31:12 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

Loading...

Loading...