UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 84 of 841

NXP Semiconductors

UM10360

Chapter 6: LPC176x/5x Nested Vectored Interrupt Controller (NVIC)

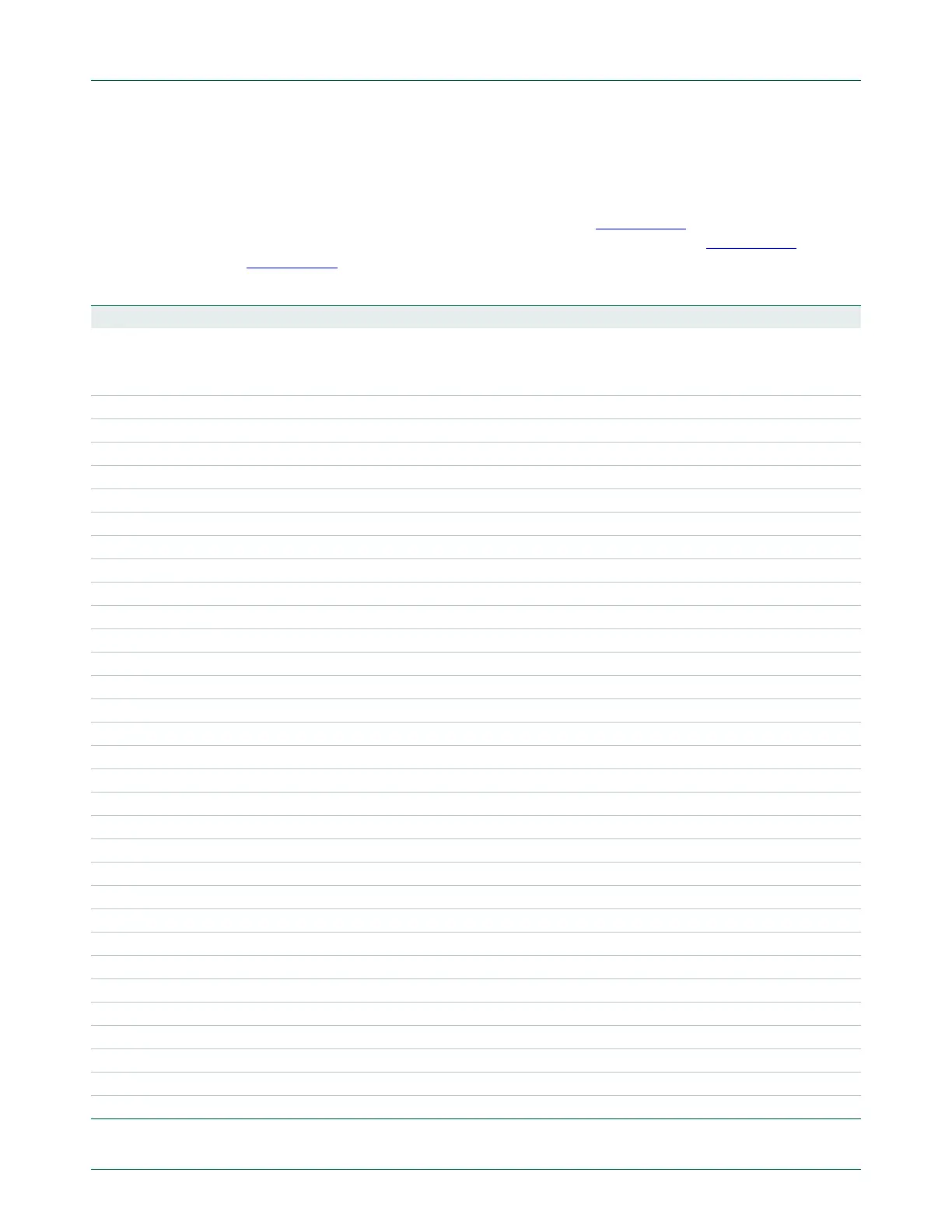

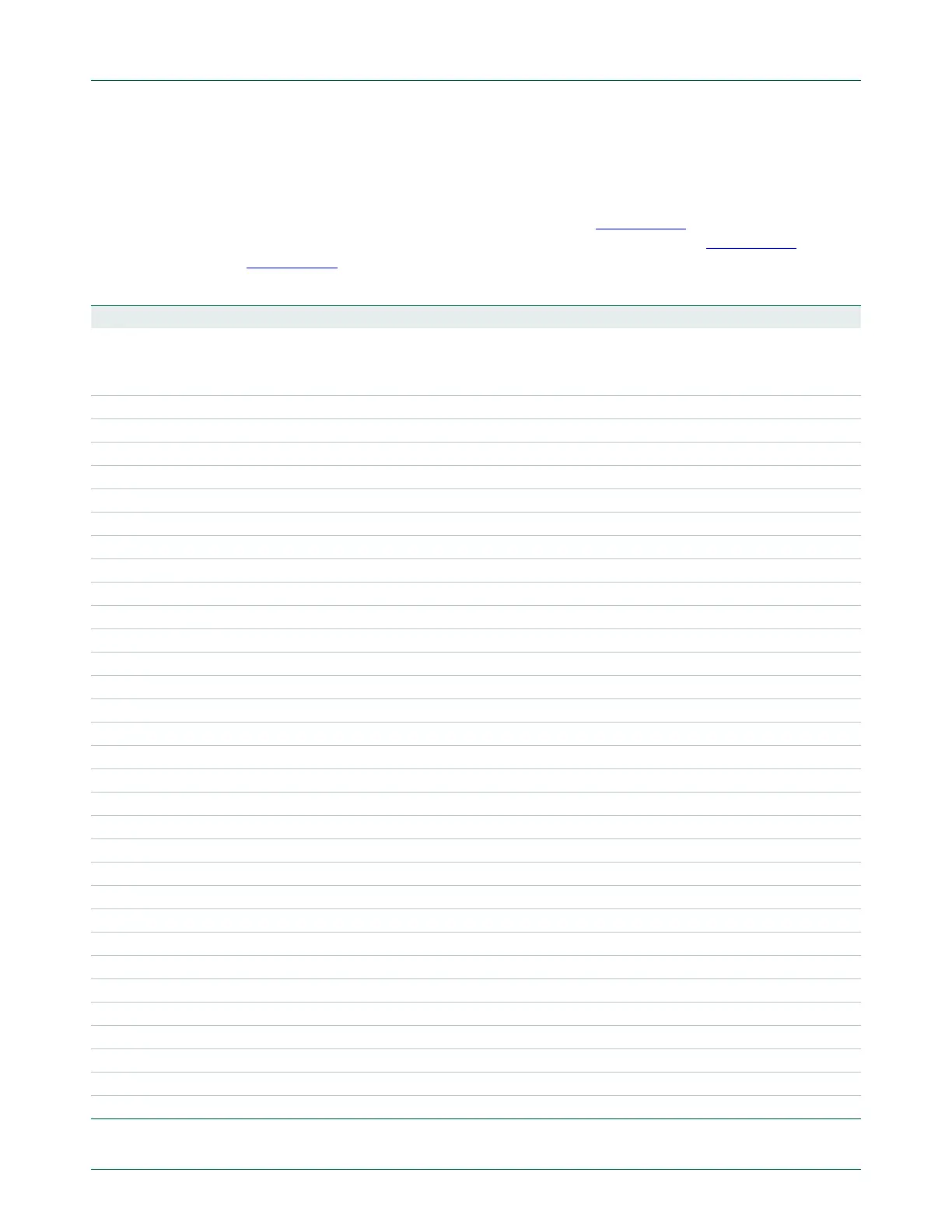

6.5.7 Interrupt Clear-Pending Register 0 register (ICPR0 - 0xE000 E280)

The ICPR0 register allows clearing the pending state of the first 32 peripheral interrupts,

or for reading the pending state of those interrupts. The remaining interrupts can have

their pending state cleared via the ICPR1 register (Section 6.5.8

). Setting the pending

state of interrupts is done through the ISPR0 and ISPR1 registers (Section 6.5.5

and

Section 6.5.6

).

Table 58. Interrupt Clear-Pending Register 0 register (ICPR0 - 0xE000 E280)

Bit Name Function

0 ICP_WDT Watchdog Timer Interrupt Pending clear.

Write: writing 0 has no effect, writing 1 changes the interrupt state to not pending.

Read: 0 indicates that the interrupt is not pending, 1 indicates that the interrupt is pending.

1 ICP_TIMER0 Timer 0 Interrupt Pending clear. See functional description for bit 0.

2 ICP_TIMER1 Timer 1. Interrupt Pending clear. See functional description for bit 0.

3 ICP_TIMER2 Timer 2 Interrupt Pending clear. See functional description for bit 0.

4 ICP_TIMER3 Timer 3 Interrupt Pending clear. See functional description for bit 0.

5 ICP_UART0 UART0 Interrupt Pending clear. See functional description for bit 0.

6 ICP_UART1 UART1 Interrupt Pending clear. See functional description for bit 0.

7 ICP_UART2 UART2 Interrupt Pending clear. See functional description for bit 0.

8 ICP_UART3 UART3 Interrupt Pending clear. See functional description for bit 0.

9 ICP_PWM PWM1 Interrupt Pending clear. See functional description for bit 0.

10 ICP_I2C0 I

2

C0 Interrupt Pending clear. See functional description for bit 0.

11 ICP_I2C1 I

2

C1 Interrupt Pending clear. See functional description for bit 0.

12 ICP_I2C2 I

2

C2 Interrupt Pending clear. See functional description for bit 0.

13 ICP_SPI SPI Interrupt Pending clear. See functional description for bit 0.

14 ICP_SSP0 SSP0 Interrupt Pending clear. See functional description for bit 0.

15 ICP_SSP1 SSP1 Interrupt Pending clear. See functional description for bit 0.

16 ICP_PLL0 PLL0 (Main PLL) Interrupt Pending clear. See functional description for bit 0.

17 ICP_RTC Real Time Clock (RTC) Interrupt Pending clear. See functional description for bit 0.

18 ICP_EINT0 External Interrupt 0 Interrupt Pending clear. See functional description for bit 0.

19 ICP_EINT1 External Interrupt 1 Interrupt Pending clear. See functional description for bit 0.

20 ICP_EINT2 External Interrupt 2 Interrupt Pending clear. See functional description for bit 0.

21 ICP_EINT3 External Interrupt 3 Interrupt Pending clear. See functional description for bit 0.

22 ICP_ADC ADC Interrupt Pending clear. See functional description for bit 0.

23 ICP_BOD BOD Interrupt Pending clear. See functional description for bit 0.

24 ICP_USB USB Interrupt Pending clear. See functional description for bit 0.

25 ICP_CAN CAN Interrupt Pending clear. See functional description for bit 0.

26 ICP_DMA GPDMA Interrupt Pending clear. See functional description for bit 0.

27 ICP_I2S I

2

S Interrupt Pending clear. See functional description for bit 0.

28 ICP_ENET Ethernet Interrupt Pending clear. See functional description for bit 0.

29 ICP_RIT Repetitive Interrupt Timer Interrupt Pending clear. See functional description for bit 0.

30 ICP_MCPWM Motor Control PWM Interrupt Pending clear. See functional description for bit 0.

31 ICP_QEI Quadrature Encoder Interface Interrupt Pending clear. See functional description for bit 0.

Loading...

Loading...