UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 303 of 841

NXP Semiconductors

UM10360

Chapter 14: LPC176x/5x UART0/2/3

select the right value for UnDLL and UnDLM can be found later in this chapter, see

Section 14.4.12

.

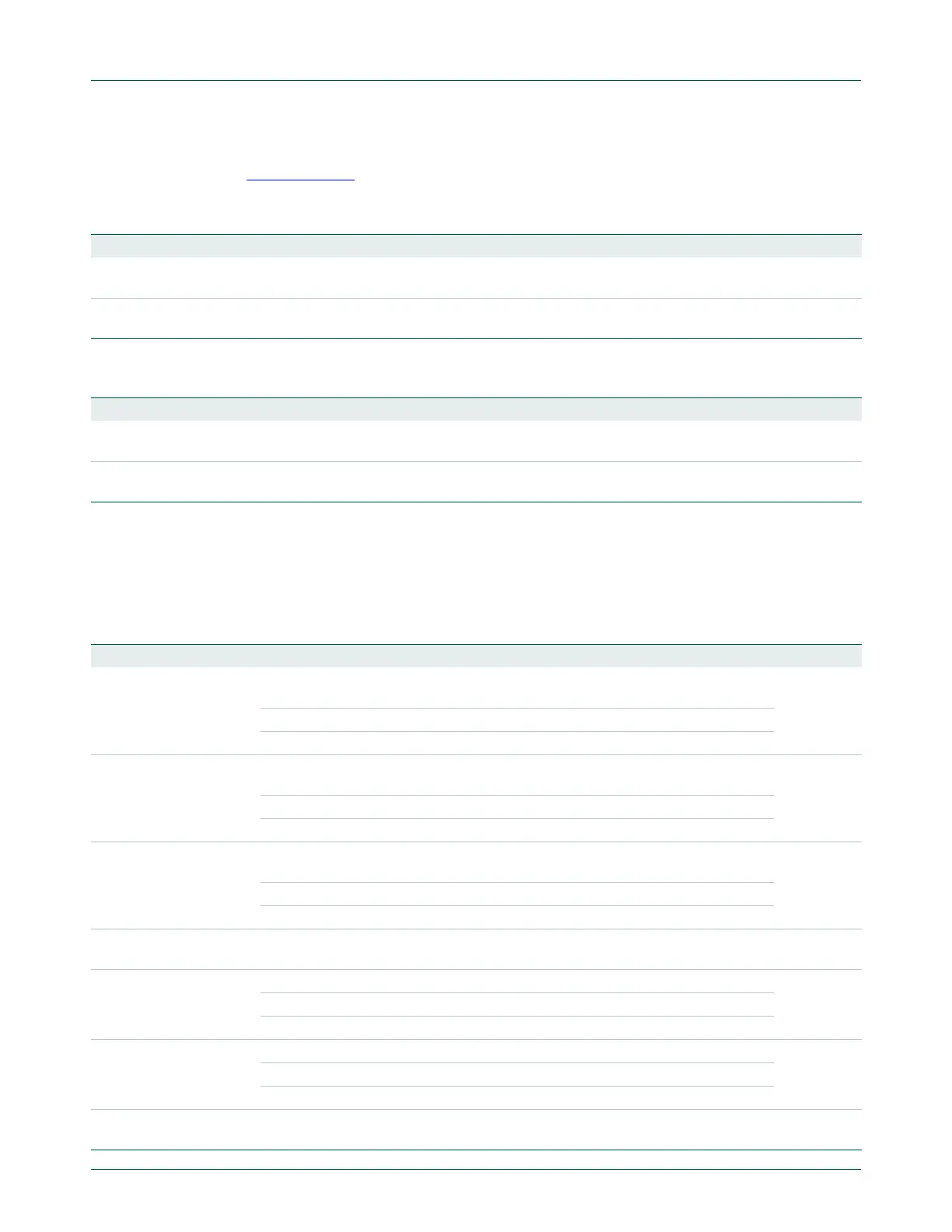

14.4.4 UARTn Interrupt Enable Register (U0IER - 0x4000 C004, U2IER -

0x4009 8004, U3IER - 0x4009 C004 when DLAB = 0)

The UnIER is used to enable the three UARTn interrupt sources.

Table 273: UARTn Divisor Latch LSB register (U0DLL - address 0x4000 C000, U2DLL - 0x4009 8000, U3DLL -

0x4009 C000 when DLAB = 1) bit description

Bit Symbol Description Reset Value

7:0 DLLSB The UARTn Divisor Latch LSB Register, along with the UnDLM register, determines the

baud rate of the UARTn.

0x01

31:8 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

Table 274: UARTn Divisor Latch MSB register (U0DLM - address 0x4000 C004, U2DLM - 0x4009 8004, U3DLM -

0x4009 C004 when DLAB = 1) bit description

Bit Symbol Description Reset Value

7:0 DLMSB The UARTn Divisor Latch MSB Register, along with the U0DLL register, determines the

baud rate of the UARTn.

0x00

31:8 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

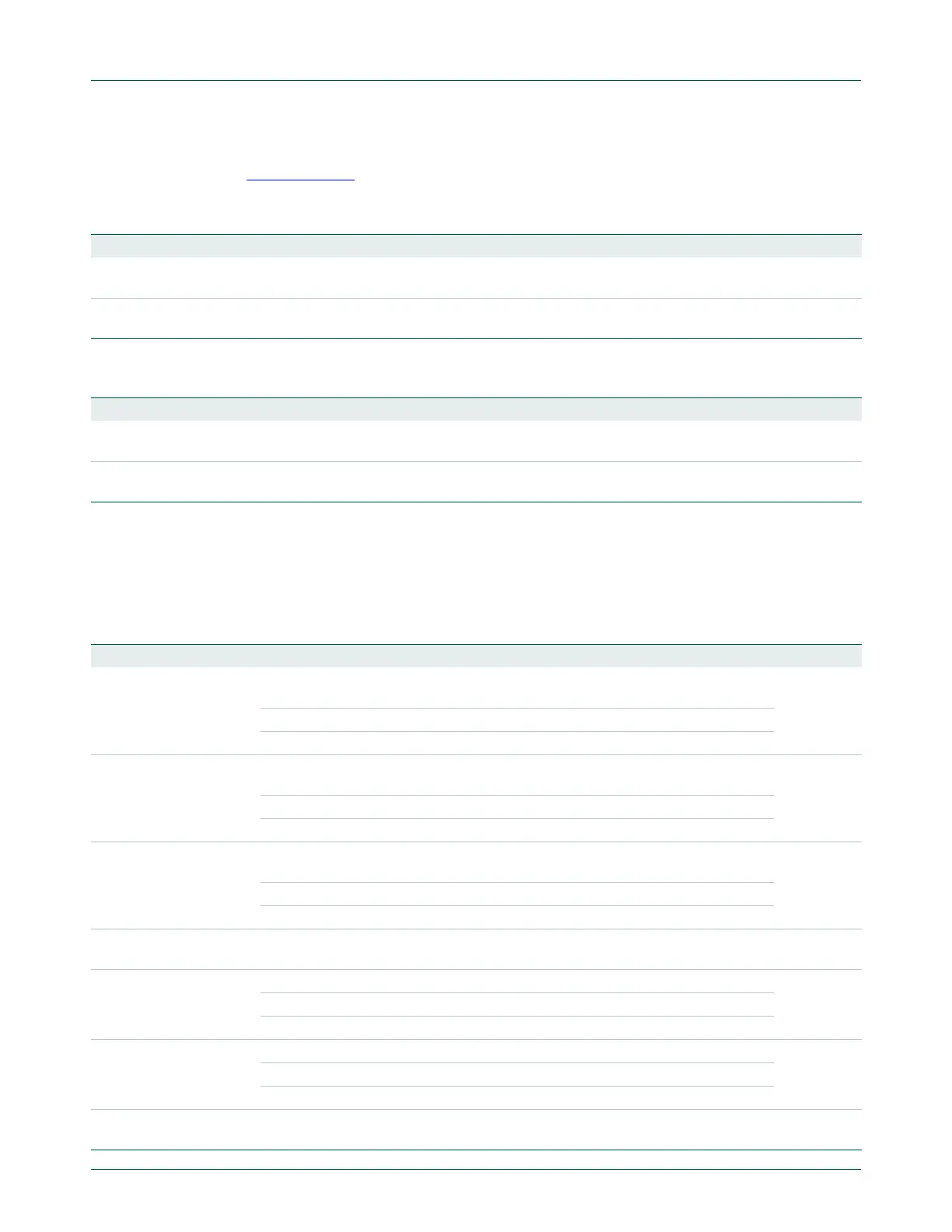

Table 275: UARTn Interrupt Enable Register (U0IER - address 0x4000 C004, U2IER - 0x4009 8004, U3IER -

0x4009 C004 when DLAB = 0) bit description

Bit Symbol Value Description Reset Value

0 RBR Interrupt

Enable

Enables the Receive Data Available interrupt for UARTn. It also controls

the Character Receive Time-out interrupt.

0

0 Disable the RDA interrupts.

1 Enable the RDA interrupts.

1 THRE Interrupt

Enable

Enables the THRE interrupt for UARTn. The status of this can be read

from UnLSR[5].

0

0 Disable the THRE interrupts.

1 Enable the THRE interrupts.

2 RX Line Status

Interrupt Enable

Enables the UARTn RX line status interrupts. The status of this interrupt

can be read from UnLSR[4:1].

0

0 Disable the RX line status interrupts.

1 Enable the RX line status interrupts.

7:3 - Reserved, user software should not write ones to reserved bits. The value

read from a reserved bit is not defined.

NA

8 ABEOIntEn Enables the end of auto-baud interrupt. 0

0 Disable end of auto-baud Interrupt.

1 Enable end of auto-baud Interrupt.

9 ABTOIntEn Enables the auto-baud time-out interrupt. 0

0 Disable auto-baud time-out Interrupt.

1 Enable auto-baud time-out Interrupt.

31:10 - Reserved, user software should not write ones to reserved bits. The value

read from a reserved bit is not defined.

NA

Loading...

Loading...