UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 642 of 841

NXP Semiconductors

UM10360

Chapter 32: LPC176x/5x Flash memory interface and programming

32.10.2 Algorithm and procedure for signature generation

Signature generation

A signature can be generated for any part of the flash contents. The address range to be

used for signature generation is defined by writing the start address to the FMSSTART

register, and the stop address to the FMSSTOP register.

The signature generation is started by writing a ‘1’ to FMSSTOP.MISR_START. Starting

the signature generation is typically combined with defining the stop address, which is

done in another field FMSSTOP.FMSSTOP of the same register.

The time that the signature generation takes is proportional to the address range for which

the signature is generated. Reading of the flash memory for signature generation uses a

self-timed read mechanism and does not depend on any configurable timing settings for

the flash. A safe estimation for the duration of the signature generation is:

Duration = int( (60 / tcy) + 3 ) x (FMSSTOP - FMSSTART + 1)

When signature generation is triggered via software, the duration is in AHB clock cycles,

and tcy is the time in ns for one AHB clock. The SIG_DONE bit in FMSTAT can be polled

by software to determine when signature generation is complete.

If signature generation is triggered via JTAG, the duration is in JTAG tck cycles, and tcy is

the time in ns for one JTAG clock. Polling the SIG_DONE bit in FMSTAT is not possible in

this case.

After signature generation, a 128-bit signature can be read from the FMSW0 to FMSW3

registers. The 128-bit signature reflects the corrected data read from the flash. The 128-bit

signature reflects flash parity bits and check bit values.

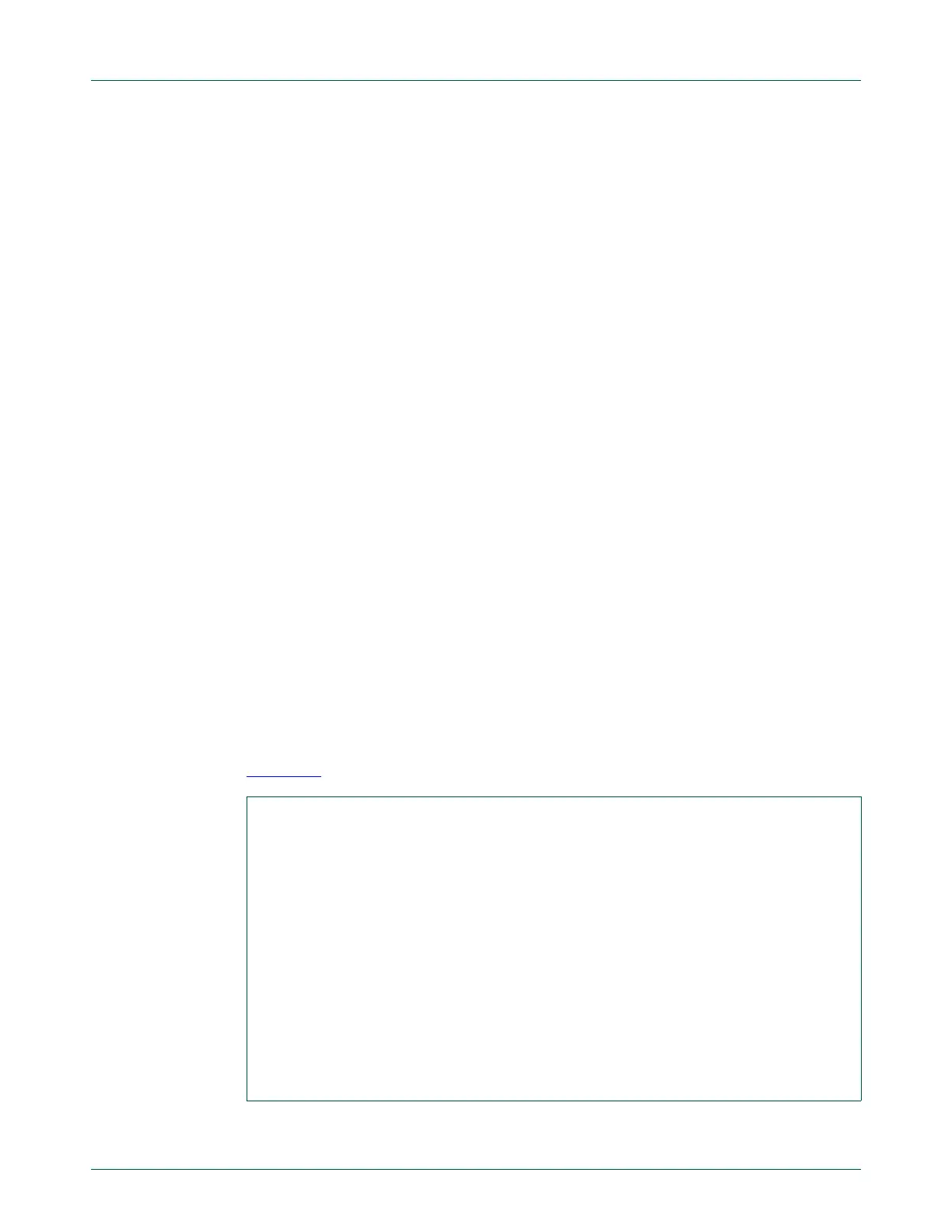

Content verification

The signature as it is read from the FMSW0 to FMSW3 registers must be equal to the

reference signature. The algorithms to derive the reference signature is given in

Figure 139

.

Fig 139. Algorithm for generating a 128 bit signature

sign = 0

FOR address = FMSTART.FMSTART TO FMSTOP.FMSTOP

{

FOR i = 0 TO 126

nextSign[i] = f_Q[address][i] XOR sign[i+1]

nextSign[127] = f_Q[address][127] XOR sign[0] XOR sign[2] XOR

sign[27] XOR sign[29]

sign = nextSign

}

signature128 = sign

Loading...

Loading...