UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 20 December 2013 715 of 841

NXP Semiconductors

UM10360

Chapter 34: Appendix: Cortex-M3 user guide

34.2.10 Miscellaneous instructions

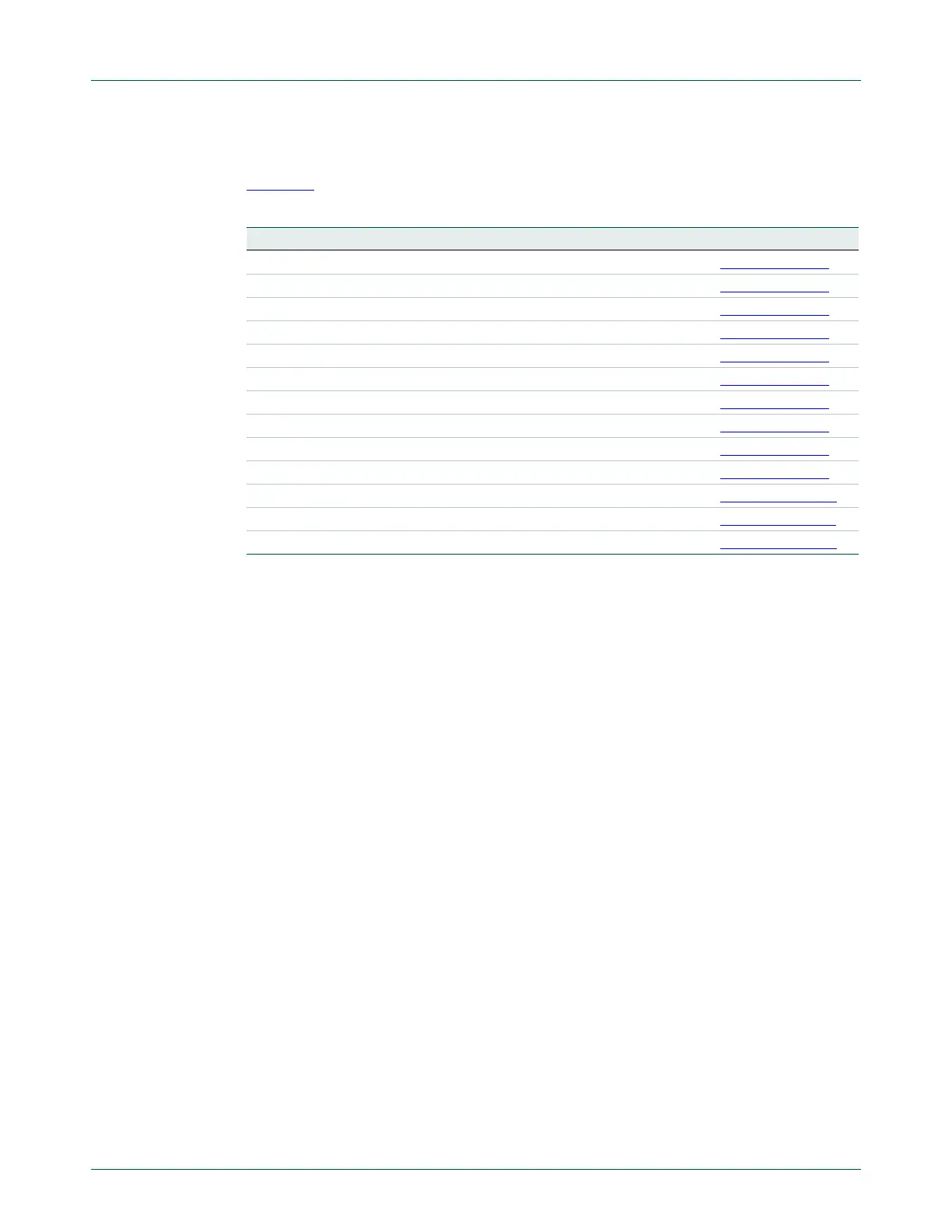

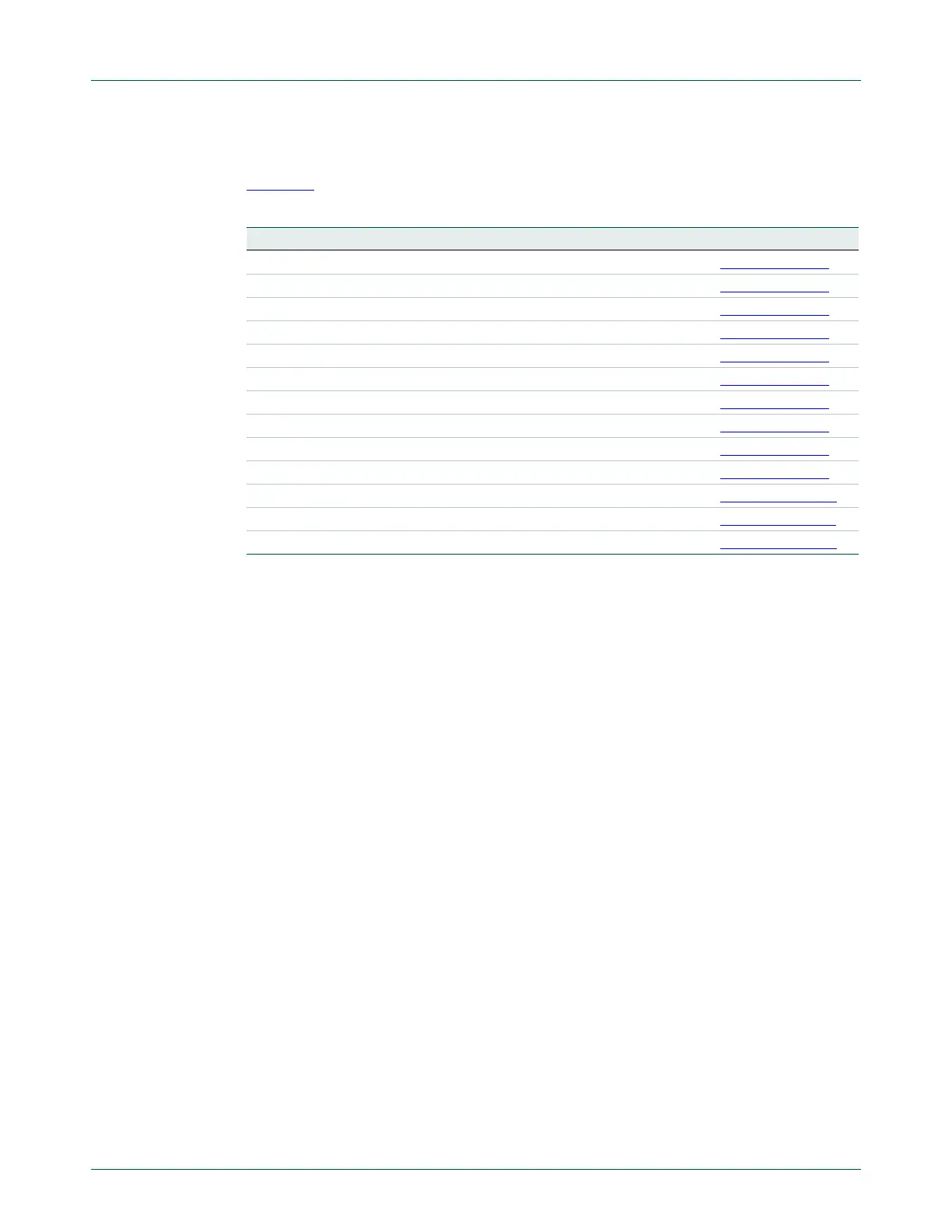

Table 624 shows the remaining Cortex-M3 instructions:

Table 624. Miscellaneous instructions

Mnemonic Brief description See

BKPT

Breakpoint Section 34.2.10.1

CPSID

Change Processor State, Disable Interrupts Section 34.2.10.2

CPSIE

Change Processor State, Enable Interrupts Section 34.2.10.2

DMB

Data Memory Barrier Section 34.2.10.3

DSB

Data Synchronization Barrier Section 34.2.10.4

ISB

Instruction Synchronization Barrier Section 34.2.10.5

MRS

Move from special register to register Section 34.2.10.6

MSR

Move from register to special register Section 34.2.10.7

NOP

No Operation Section 34.2.10.8

SEV

Send Event Section 34.2.10.9

SVC

Supervisor Call Section 34.2.10.10

WFE

Wait For Event Section 34.2.10.11

WFI

Wait For Interrupt Section 34.2.10.12

Loading...

Loading...