UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 550 of 841

NXP Semiconductors

UM10360

Chapter 26: LPC176x/5x Quadrature Encoder Interface (QEI)

26.6 Register description

26.6.1 Register summary

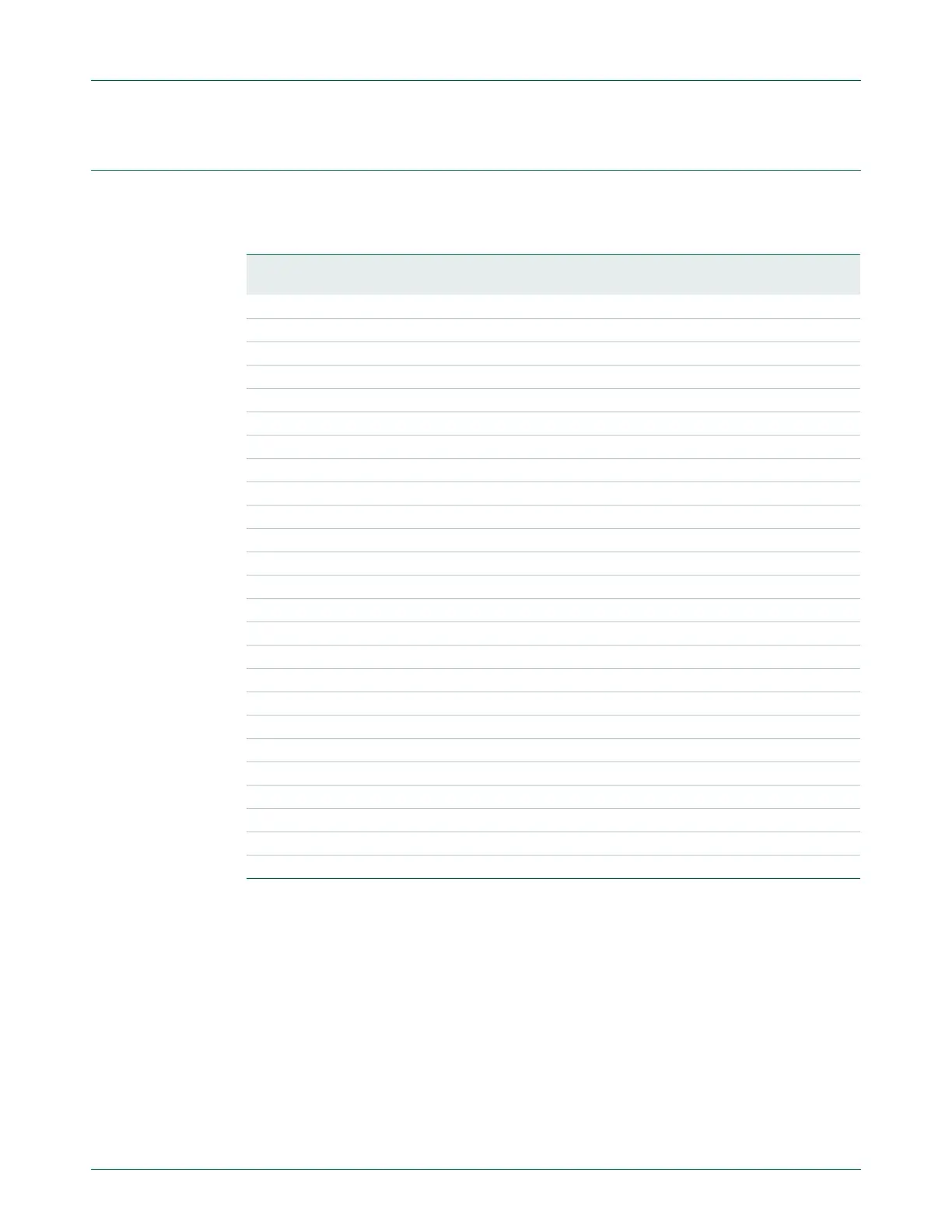

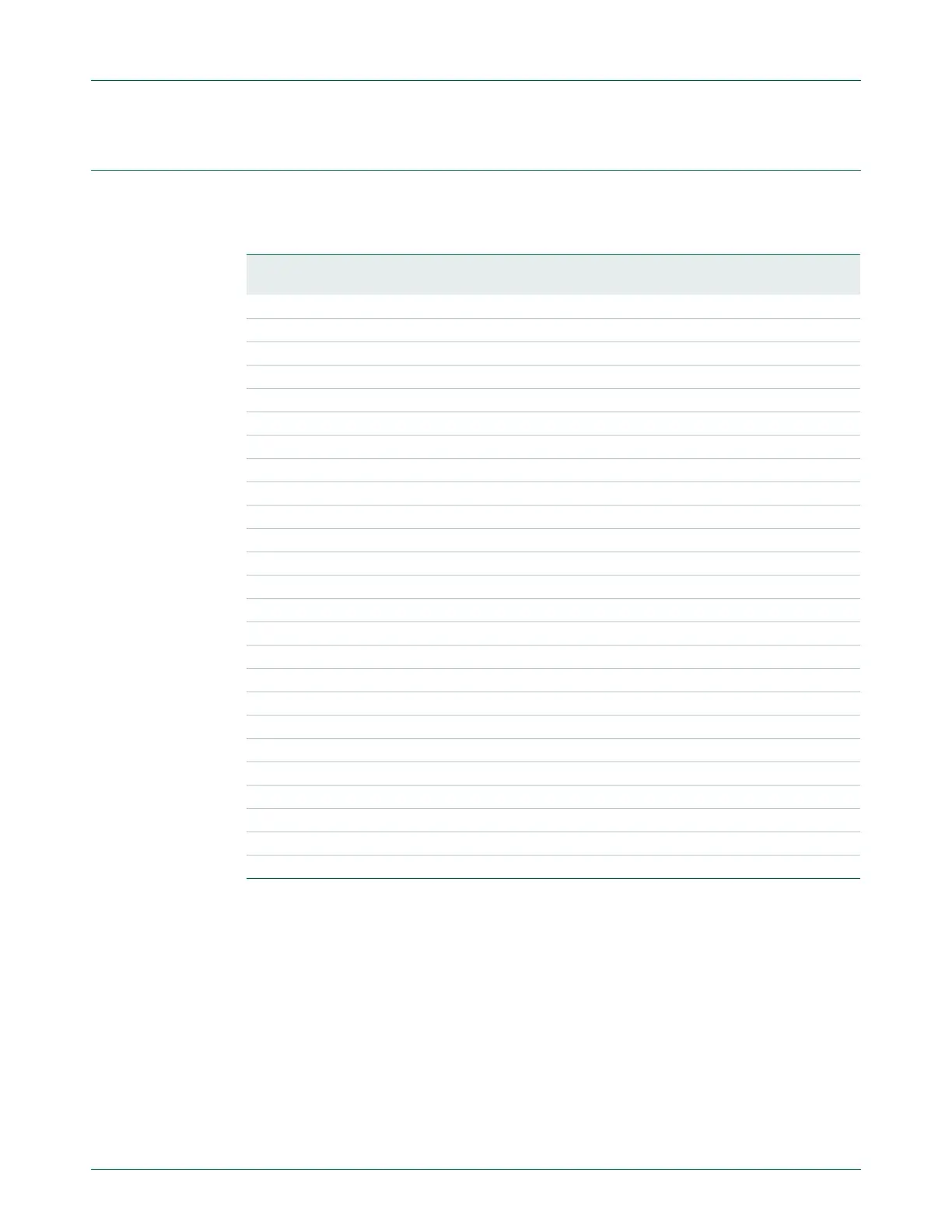

Table 483. QEI Register summary

Name Description Access Reset

value

Address

Control registers

QEICON Control register WO 0 0x400B C000

QEICONF Configuration register R/W 0 0x400B C008

QEISTAT Encoder status register RO 0 0x400B C004

Position, index, and timer registers

QEIPOS Position register RO 0 0x400B C00C

QEIMAXPOS Maximum position register R/W 0 0x400B C010

CMPOS0 position compare register 0 R/W 0 0x400B C014

CMPOS1 position compare register 1 R/W 0 0x400B C018

CMPOS2 position compare register 2 R/W 0 0x400B C01C

INXCNT Index count register RO 0 0x400B C020

INXCMP Index compare register R/W 0 0x400B C024

QEILOAD Velocity timer reload register R/W 0 0x400B C028

QEITIME Velocity timer register RO 0 0x400B C02C

QEIVEL Velocity counter register RO 0 0x400B C030

QEICAP Velocity capture register RO 0 0x400B C034

VELCOMP Velocity compare register R/W 0 0x400B C038

FILTER Digital filter register R/W 0 0x400B C03C

Interrupt registers

QEIINTSTAT Interrupt status register RO 0 0x400B CFE0

QEISET Interrupt status set register WO 0 0x400B CFEC

QEICLR Interrupt status clear register WO 0 0x400B CFE8

QEIIE Interrupt enable register RO 0 0x400B CFE4

QEIIES Interrupt enable set register WO 0 0x400B CFDC

QEIIEC Interrupt enable clear register WO 0 0x400B CFD8

Loading...

Loading...