UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 410 of 841

NXP Semiconductors

UM10360

Chapter 17: LPC176x/5x SPI

In Master mode, this register must be an even number greater than or equal to 8.

Violations of this can result in unpredictable behavior. The SPI0 SCK rate may be

calculated as: PCLK_SPI / SPCCR0 value. The SPI peripheral clock is determined by the

PCLKSEL0 register contents for PCLK_SPI as described in Section 4.7.3

.

In Slave mode, the SPI clock rate provided by the master must not exceed 1/8 of the SPI

peripheral clock selected in Section 4.7.3

. The content of the S0SPCCR register is not

relevant.

17.7.5 SPI Test Control Register (SPTCR - 0x4002 0010)

Note that the bits in this register are intended for functional verification only. This register

should not be used for normal operation.

17.7.6 SPI Test Status Register (SPTSR - 0x4002 0014)

Note: The bits in this register are intended for functional verification only. This register

should not be used for normal operation.

This register is a replication of the SPI Status Register. The difference between the

registers is that a read of this register will not start the sequence of events required to

clear these status bits. A write to this register will set an interrupt if the write data for the

respective bit is a 1.

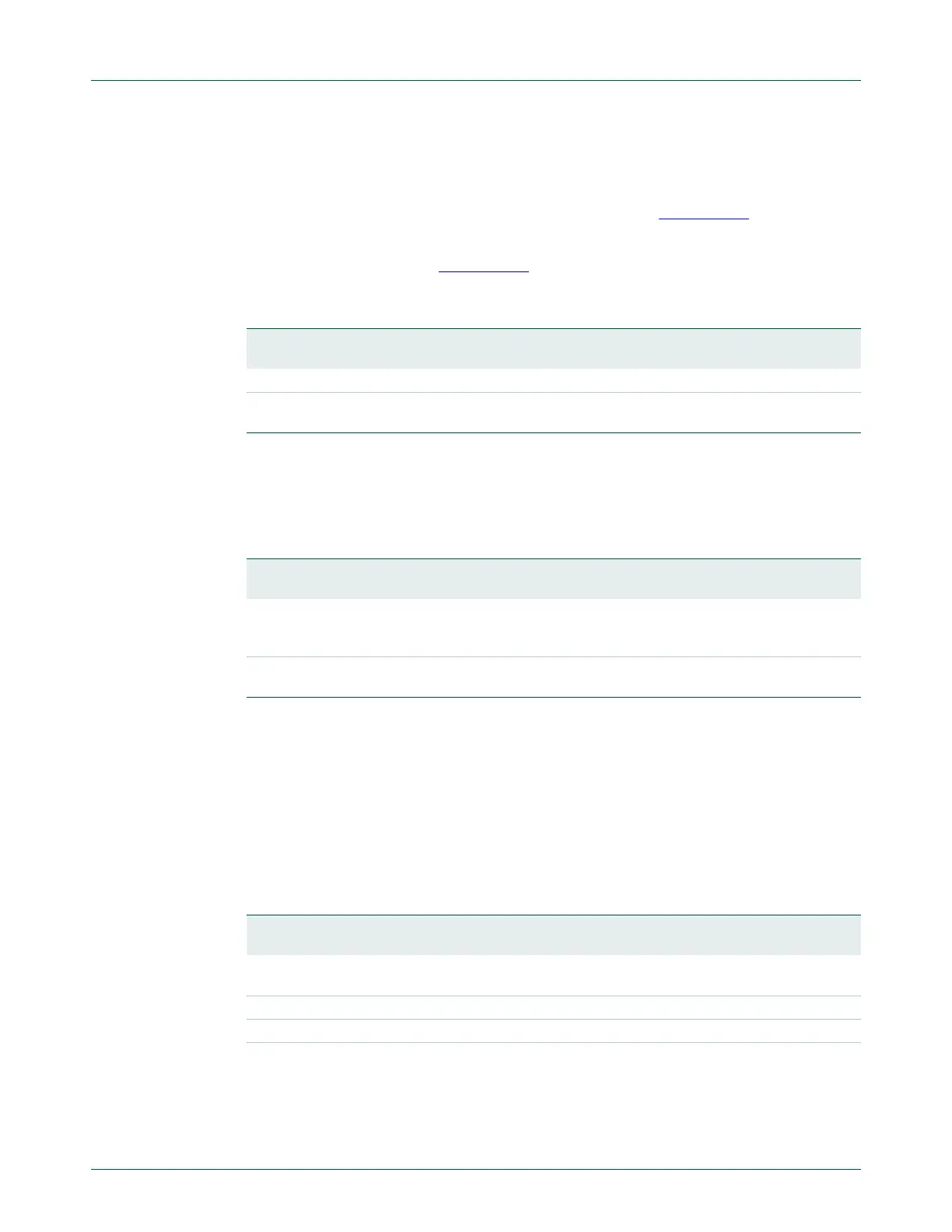

Table 364: SPI Clock Counter Register (S0SPCCR - address 0x4002 000C) bit description

Bit Symbol Description Reset

Value

7:0 Counter SPI0 Clock counter setting. 0x00

31:8 - Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

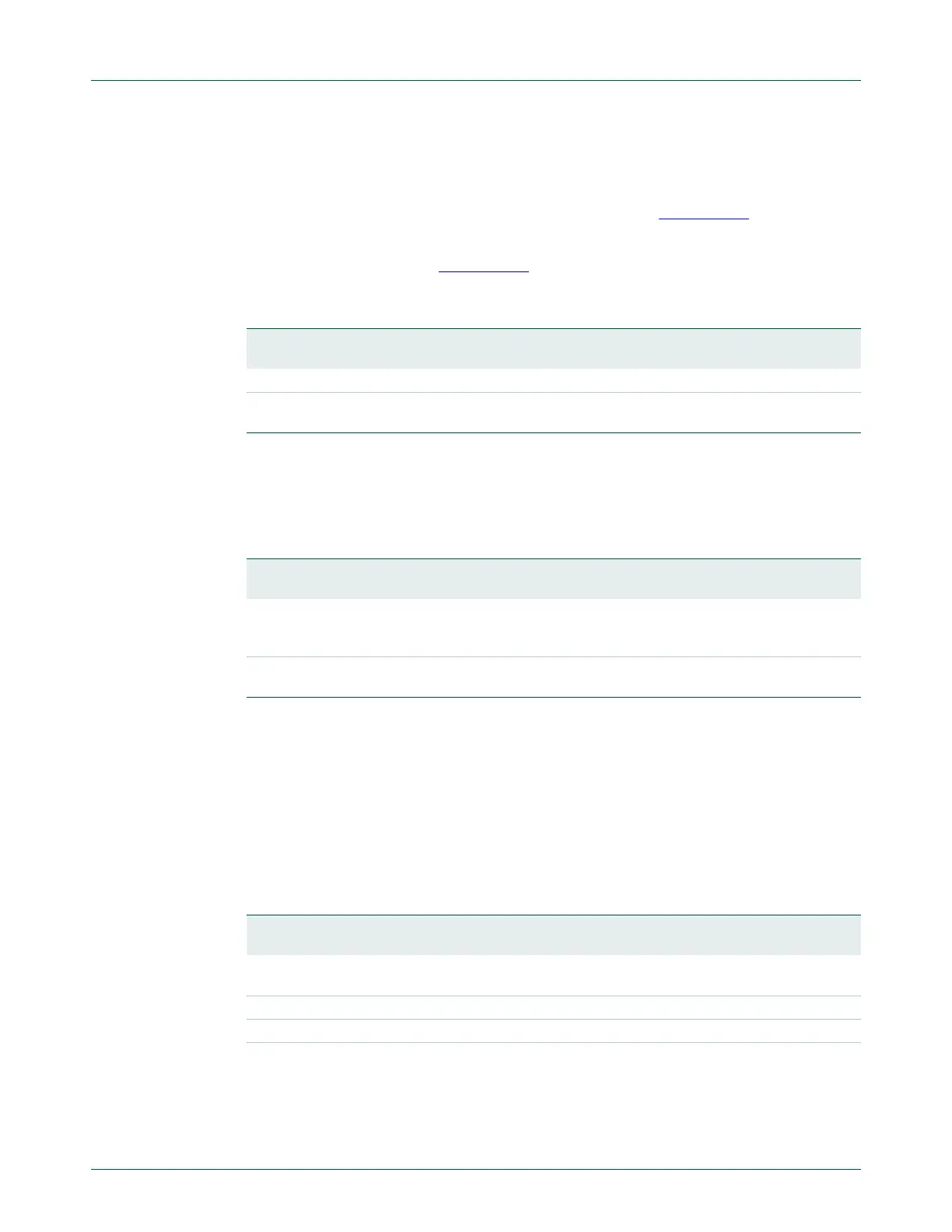

Table 365: SPI Test Control Register (SPTCR - address 0x4002 0010) bit description

Bit Symbol Description Reset

Value

0 Test SPI test mode. When 0, the SPI operates normally. When 1, SCK will

always be on, independent of master mode select, and data availability

setting.

NA

31:1 - Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

Table 366: SPI Test Status Register (SPTSR - address 0x4002 0014) bit description

Bit Symbol Description Reset

Value

2:0 - Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

3 ABRT Slave abort. 0

4 MODF Mode fault. 0

5 ROVR Read overrun. 0

Loading...

Loading...